# Metal oxide-graphene field-effect transistor: interface trap density extraction model

Faraz Najam<sup>1</sup>, Kah Cheong Lau<sup>1,2</sup>, Cheng Siong Lim<sup>1</sup>, Yun Seop Yu<sup>3</sup> and Michael Loong Peng Tan<sup>\*1</sup>

#### Full Research Paper

#### Address:

<sup>1</sup>Faculty of Electrical Engineering, Universiti Teknologi Malaysia, 81310 Skudai, Johor, Malaysia, <sup>2</sup>Intel Technology Sdn Bhd, Bayan Lepas Free Industrial Zone, Phase 3, Halaman Kampung Jawa, 11900, Bayan Lepas, Pulau Pinang, 11900, Malaysia and <sup>3</sup>Department of Electrical, Electronic and Control Engineering and IITC, Hankyong National University, Anseong 456-749, Korea

#### Email:

Michael Loong Peng Tan\* - michael@utm.my

\* Corresponding author

#### Keywords:

drain current compact model; interface trap distribution; metal-oxide-graphene field-effect transistor (MOGFET); surface potential

Beilstein J. Nanotechnol. **2016**, 7, 1368–1376. doi:10.3762/bjnano.7.128

Received: 24 May 2016 Accepted: 06 September 2016 Published: 30 September 2016

Associate Editor: N. Motta

© 2016 Najam et al.; licensee Beilstein-Institut. License and terms: see end of document.

Open Access

#### Abstract

A simple to implement model is presented to extract interface trap density of graphene field effect transistors. The presence of interface trap states detrimentally affects the device drain current–gate voltage relationship  $I_{\rm ds}$ – $V_{\rm gs}$ . At the moment, there is no analytical method available to extract the interface trap distribution of metal-oxide-graphene field effect transistor (MOGFET) devices. The model presented here extracts the interface trap distribution of MOGFET devices making use of available experimental capacitance–gate voltage  $C_{\rm tot}$ – $V_{\rm gs}$  data and a basic set of equations used to define the device physics of MOGFET devices. The model was used to extract the interface trap distribution of 2 experimental devices. Device parameters calculated using the extracted interface trap distribution from the model, including surface potential, interface trap charge and interface trap capacitance compared very well with their respective experimental counterparts. The model enables accurate calculation of the surface potential affected by trap charge. Other models ignore the effect of trap charge and only calculate the ideal surface potential. Such ideal surface potential when used in a surface potential based drain current model will result in an inaccurate prediction of the drain current. Accurate calculation of surface potential that can later be used in drain current model is highlighted as a major advantage of the model.

#### Introduction

Graphene has recently attracted a lot of attention. Its 2D nature along with its significantly high carrier mobility ( $\approx 15,000 \text{ cm}^2/(\text{V}\cdot\text{s})$ ) make it an ideal material to replace silicon

[1] in the more than Moore era. During deposition of the dielectric layer on graphene as well as from deposition of graphene on the substrate defects may be formed in the film resulting in the

presence of trap states;  $D_{\rm it}$  states (cm<sup>-2</sup>·eV<sup>-1</sup>) at the interface between the dielectric layer and graphene channel [2,3]. These trap states trap mobile carriers degrading the gate field modulation effect, thereby resulting in degraded surface potential.

Popular metal-oxide-graphene field-effect transistor (MOGFET) models do not take into account the detrimental effect of  $D_{\rm it}$  states on device surface potential [4,5]. Zebrev et al. [6], recently presented a model that takes into account the effect of  $D_{\rm it}$  states on the device current. A similar approach has been used by [7]. However, Zebrev's drain current expression is based on the assumption of presence of constant  $D_{\rm it}$  states over the entire energy range of operation of the device. The assumption does not work generally; recently, significantly varying  $D_{\rm it}$  distribution has been reported for metal-oxide-graphene (MOG) capacitors [8]. This suggests the need for a model that can analytically calculate the interface trap density of MOGFET devices that could later be used in drain current  $I_{\rm ds}$  models for efficient  $I_{\rm ds}$  performance prediction.

This work presents a method to extract interface trap density of MOGFET with the help of device  $C_{\rm tot}$ – $V_{\rm gs}$  data. Basic equations and parameters needed to extract interface trap density are explained below. Extraction and verification of extracted trap density is explained following the section below.

# Basic equations and parameters Basic equations

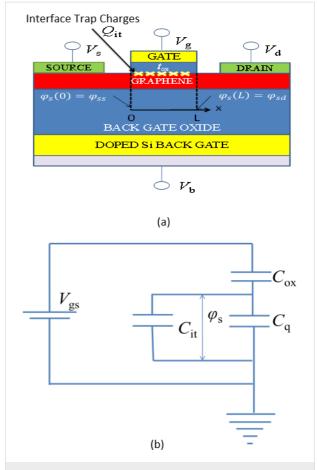

Figure 1a shows the schematic of a typical MOGFET. The channel consists of monolayer graphene with length L deposited on a  $\mathrm{SiO}_2$  layer with a p-type doped silicon substrate as the backgate (only top-gated monolayer MOGFET is considered in this work). The gate stack consists of a dielectric layer with thickness  $t_{\mathrm{ox}}$  and a metal gate.  $Q_{\mathrm{it}}$  in Figure 1a refers to the interface trap charge found at the dielectric/channel interface. Figure 1b shows the equivalent capacitive circuit of the typical capacitances in the MOGFET device. In a MOGFET top gate capacitance  $C_{\mathrm{ox}}$  is in series with the parallel combination of interface trap capacitance  $C_{\mathrm{it}}$  which originates from the presence of  $D_{\mathrm{it}}$  states, and  $C_{\mathrm{q}}$  the quantum capacitance.

$C_q$  is a graphene material property and is given by [9],

$$C_{\rm q} = \sqrt{{C_{\rm qi}}^2 + (\beta_{\rm g} q \phi_{\rm s})^2}$$

(1)

where, q is the charge on an electron,  $\varphi_s$  is surface potential,

$$\beta_{\rm g} = \frac{2q^2}{\pi h^2 v_{\rm f}^2},$$

**Figure 1:** (a) Schematic of MOGFET device. (b) Equivalent capacitive circuit of typical capacitances in MOGFET.

$\hbar$  is the Planck's constant,  $v_f$  is the fermi velocity  $(1 \times 10^8 \text{ cm}^2/(\text{V} \cdot \text{s}))$ ,  $C_{qi}$  is a fitting factor independent of  $\phi_s$ , and accounts for the finite  $C_q$  observed at Dirac point (DP) (at which the fermi level  $E_f = q\phi_s = 0 = E_D$ , where  $E_D$  is the energy (eV) at DP).

The total capacitance  $C_{\text{tot}}$  of MOGFET is given by,

$$C_{\text{tot}} = \frac{C_{\text{ox}} \left( C_{\text{q}} + C_{\text{it}} \right)}{C_{\text{ox}} + C_{\text{q}} + C_{\text{it}}}.$$

(2)

Applying the capacitor divider relation to Figure 1b, the surface potential  $\phi_S$  of MOGFET is given by,

$$\varphi_{\rm s} = \frac{(V_{\rm gs} - V_{\rm DP} - V_{\rm c})C_{\rm ox}}{C_{\rm ox} + C_{\rm ot} + C_{\rm it}},$$

(3)

where  $V_{\rm gs}$  is the gate voltage,  $V_{\rm DP}$  is the gate voltage at DP known to be caused by the gate-metal/graphene workfunction

difference [10], and/or interface trap states [11], and  $V_{\rm c}$  is the channel voltage drop due to the applied drain bias  $V_{\rm ds}$  with  $V_{\rm c}=0$  at the source end and  $V_{\rm c}=V_{\rm ds}$  at the drain end.

Solving self-consistently for  $\varphi_s$  in Equation 3 and  $C_q = (\beta_g q \varphi_s)$ ,  $\varphi_s$  is given by Equation 4,

$$\phi_{s} = \frac{-(C_{ox} + C_{it})}{\pm 2\beta_{g}q} + \frac{\sqrt{(C_{ox} + C_{it})^{2} \pm 4\beta_{g}q(V_{gs} - V_{DP} - V_{C})C_{ox}}}{\pm 2\beta_{g}q} \tag{4}$$

Here, the positive (negative) sign applies when  $(V_{\rm gs}-V_{\rm DP}-V_{\rm c})$   $C_{\rm ox}>0$  (< 0). The sum of  $C_{\rm q}+C_{\rm it}$  in Equation 2 and Equation 3 can be labeled as  $C_{\rm x}$ . The next few paragraphs explain the procedure for extraction of experimental  $\phi_{\rm s}$ ,  $C_{\rm q}$ ,  $C_{\rm it}$  and  $Q_{\rm it}$  parameters of two sample MOGFET devices which are then used in extraction of their  $D_{\rm it}$  distributions explained in the section "Extraction of interface trap states".

### Experimental $\varphi_s$ , $C_{it}$ , and $Q_{it}$ extraction

Surface potential  $\varphi_s$  and  $C_{it}$  were extracted for two MOGFET devices using experimental  $C_{tot}$ – $V_{gs}$  data (from herein referred as  $C_{tot\_exp}$ ) taken from Device 1 [7], and device 2 [12] (with back-gate bias = 0 V, and  $V_{ds}$  = 0). The extracted  $\varphi_s$  and  $C_{it}$  parameters obtained using experimental  $C_{tot\_exp}$  data will be referred to as  $\varphi_{s\_exp}$  and  $C_{it\_exp}$ . The device parameters for both the devices are mentioned in Table 1.

| Table 1: Device parameters for devices 1 and 2. |                                      |                            |

|-------------------------------------------------|--------------------------------------|----------------------------|

| Device                                          | Device<br>parameter                  | MOGFET reported/used value |

| Device 1 [7]                                    | Cox (µF/cm <sup>2</sup> )            | 1.98                       |

|                                                 | $V_{DP}\left(V\right)$               | 0.2                        |

|                                                 | $C_{\rm qi}$ ( $\mu {\rm F/cm^2}$ )  | 1                          |

| Device 2 [12]                                   | $C_{\rm ox}$ (µF/cm <sup>2</sup> )   | 0.76                       |

|                                                 | $V_{DP}\left(V\right)$               | 0.11                       |

|                                                 | $C_{qi}$ ( $\mu$ F/cm <sup>2</sup> ) | 1.6                        |

|                                                 |                                      |                            |

As mentioned in [12] for Device 2, the DC method used to find  $C_{\rm ox}$  involves a large amount of ambiguity due to imprecise evaluation of the back-gate capacitance [13], and consequently  $C_{\rm ox}$ . A  $C_{\rm ox}$  value of 1.00  $\mu$ F/cm² along with available  $C_{\rm q}$  and  $C_{\rm it}$  parameters from [12] in Equation 2 was found to reproduce available  $C_{\rm tot\_exp}$ , and  $C_{\rm q}$  results very well, instead of the reported value of 0.76  $\mu$ F/cm², the former is used instead in this work. The extraction procedure is described next.

$C_{\rm x}$  can be found from Equation 5 which is derived from manipulating Equation 2. Here  $C_{\rm tot}$  is the respective experimental  $C_{\rm tot}$ – $V_{\rm gs}$  data for the two experimental devices and  $C_{\rm ox}$  is their oxide capacitances mentioned in Table 1.

$$C_{\rm x} = \frac{C_{\rm ox}C_{\rm tot}}{C_{\rm ox} - C_{\rm tot}} \tag{5}$$

$C_{\rm x}$  obtained from the above equation is then substituted in Equation 3 to extract device's  $\varphi_{\rm s}$  as a function of  $V_{\rm gs}$ , with all the other parameters in Equation 3 known. The extracted  $\varphi_{\rm s}$  is referred to as  $\varphi_{\rm s\_exp}$  as device's surface potential extracted from experimental  $C_{\rm tot}-V_{\rm gs}$  data.

Once  $\varphi_{s\_exp}$  is obtained,  $C_q$  can be calculated from Equation 1. Finally, device's  $C_{it}$  can be obtained using the expression below. The extracted  $C_{it}$  is referred to as  $C_{it\_exp}$  as device's interface trap capacitance obtained from experimental  $C_{tot}$ – $V_{gs}$  data

$$C_{\text{it exp}} = C_{\text{x}} - C_{\text{q}} \tag{6}$$

By substituting  $C_{it\_exp}$  in the expression given below, device's  $Q_{it}$  can be extracted.

$$Q_{\text{it\_exp}} = \frac{1}{q} \int_{E_{\text{D}}}^{E_{\text{f}}} C_{\text{it\_exp}} dE_{\text{f}}$$

(7)

In Equation 7  $E_{\rm f} = \varphi_{\rm s\_exp}$ . The extracted  $Q_{\rm it}$  is referred to as  $Q_{\rm it\_exp}$  as the interface trap charge extracted from experimental  $C_{\rm tot}$ – $V_{\rm gs}$  data.

The relationship between  $C_{it}$  and  $Q_{it}$  is given by

$$C_{\rm it} = \frac{dQ_{\rm it}}{d\varphi_{\rm s}}.$$

(8)

#### Extraction of interface trap states

For the extraction, according to standard convention [6] acceptor and donor type traps states were considered for the n-type MOGFET, and p-type MOGFET operation, respectively.

The interface trap charge for both acceptor type and donor type trap states can be calculated from the following [11],

$$Q_{\text{it\_calc}} = q \int_{E_{D}}^{E_{f}} D_{\text{it}}(i) F_{\text{tA}(D)}(i) dE_{f}$$

(9)

$$F_{\text{tA}(i)} = \frac{1}{1 + \exp(E_{\text{tA}(i)} - E_{\text{f}}) / k_{\text{B}}T}$$

(10)

$$F_{\text{tD}(i)} = 1 - \frac{1}{1 + \exp(E_{\text{tD}(i)} - E_{\text{f}}) / k_{\text{B}}T}$$

(11)

Here, in Equation 9–11,  $Q_{\rm it\_calc}$  denotes the calculated interface trap charge,  $F_{\rm tA}$  ( $F_{\rm tD}$ ) denotes the probability of occupation of k acceptor (donor) type trap states, and  $E_{\rm tA}$  ( $E_{\rm tD}$ ) denotes the ith energy level of each of these k acceptor (donor) type trap state.  $D_{\rm it}$  is the interface trap density defined at the ith energy level.  $Q_{\rm it}$  can be found by the integral of product of all the k trap states with their respective  $F_{\rm tA}$  ( $F_{\rm tD}$ ) between  $E_{\rm D}$  and  $E_{\rm f}$ .

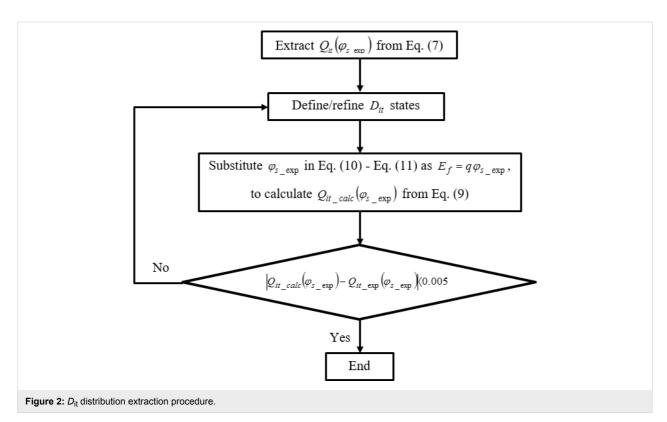

$D_{it}$  distribution extraction criteria are based on our earlier work on MoS<sub>2</sub> MOSFET [14], and are highlighted in Figure 2. The following procedure describes  $D_{it}$  extraction criteria for MOGFET devices using the two reference experimental devices. As a first step,  $Q_{it\_exp}$  and  $\phi_{s\_exp}$  values are extracted using the procedure outlined in the previous section. Next, the extracted  $\phi_{s\_exp}$  is substituted in Equation 10 and Equation 11 as  $E_f = q\phi_{s\_exp}$  to calculate  $F_{tA(D)}$  values. These  $F_{tA(D)}$  values are then used in Equation 9 to find  $Q_{it\_calc}$ . In this step and the step prior to this,  $D_{it}$  values in Equation 9 and  $E_{tA(D)}$  values in Equation 10 and Equation 11 are fitted for each energy level such that  $Q_{it\_calc}$  obtained using this procedure matches, as a function of  $\phi_{s\_exp}$ , experimental  $Q_{it\_exp}$  extracted earlier. This is indicated by step 3 of the flowchart shown in Figure 2.

If  $Q_{\rm it\_exp}$  and  $Q_{\rm it\_calc}$  values as a function of  $\varphi_{\rm s\_exp}$  match it means the fitted  $D_{\rm it}$  values used in Equation 9 to calculate  $Q_{\rm it\_calc}$  were a good fit to reproduce the extracted experimental  $Q_{\rm it\_exp}$ . This step enables us to calculate  $D_{\rm it}$  values.

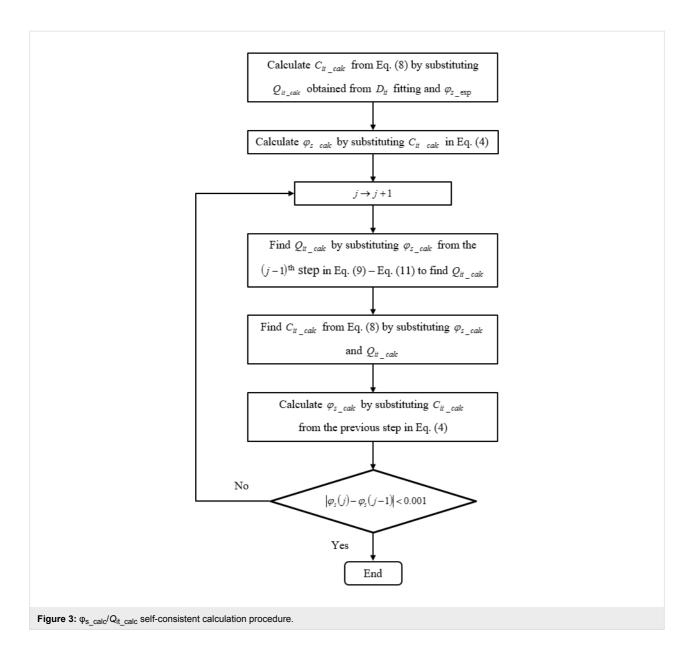

At this point, we have only calculated  $Q_{\rm it\_calc}$  as a function of  $\phi_{\rm s\_exp}$ . In order to compare parameters consistently we need to self-consistently find  $Q_{\rm it\_calc}$  as a function of  $\phi_{\rm s\_calc}$ , where  $\phi_{\rm s\_calc}$  refers to  $\phi_{\rm s}$  calculated from Equation 4 using  $C_{\rm it\_calc}$  as the input variable.  $C_{\rm it\_calc}$  refers to  $C_{\rm it}$  calculated from Equation 8 using  $Q_{\rm it\_calc}$  and  $\phi_{\rm s\_calc}$  as input variables. The self-consistent  $C_{\rm it\_calc}$ – $\phi_{\rm s\_calc}$  calculation procedure is based on our earlier works on MOSFET interface trap drain current modeling [14,15]. The procedure is highlighted in Figure 3 and is described next.

The first step is calculating  $C_{\rm it\_calc}$  from Equation 8 by substituting  $Q_{\rm it\_calc}$  obtained in the previous step (i.e., during the  $D_{\rm it}$  extraction procedure) and the earlier obtained  $\phi_{\rm s\_exp}$ . The calculated  $C_{\rm it}$  is referred to as  $C_{\rm it\_calc}$ . Calcuted  $C_{\rm it\_calc}$  is then substituted in Equation 4 to find  $\phi_{\rm s\_calc}$ . This  $\phi_{\rm s\_calc}$  is then substituted back in Equation 9–11 using the already extracted interface trap distribution to calculate  $Q_{\rm it\_calc}$ . This  $Q_{\rm it\_calc}$  along with  $\phi_{\rm s\_calc}$  obtained in the previous step is substituted back in Equation 8 to find  $C_{\rm it\_calc}$  which is then substituted in Equation 4 to find  $\phi_{\rm s\_calc}$ . This process is repeated back and forth until self-consistency is obtained between  $Q_{\rm it\_calc}/C_{\rm it\_calc}$

and  $\varphi_{s\_calc}$ . Now we can express  $Q_{it\_calc}/C_{it\_calc}$  as functions of  $\varphi_{s\_calc}$ , and in turn  $\varphi_{s\_calc}$  is calculated using  $C_{it\_calc}$ .

Interface trap distribution verification criteria simply implies that

- 1.  $Q_{it\_calc}$  (as a function of  $\varphi_{s\_calc}$ ) should match well with  $Q_{it\_exp}$  (as a function of  $\varphi_{s\_exp}$ ).

- 2.  $C_{it\_calc}$  (as a function of  $\varphi_{s\_calc}$ ) should match well with  $C_{it\_exp}$  (as a function of  $\varphi_{s\_exp}$ ).

- 3.  $\phi_s$  calc should match well with  $\phi_s$  exp.

If the respective calculated and experimental parameters are in reasonable agreement, it proves that the fitted  $D_{\rm it}$  values used to find the calculated parameters were reasonable (within a toler-

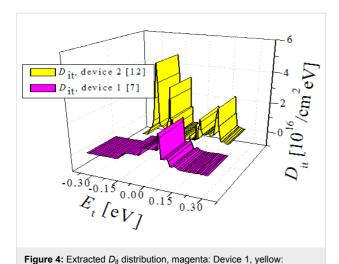

ance limit) to match well the experimental parameters. The extracted  $D_{\rm it}$  distribution is shown in Figure 4; magenta for Device 1 and yellow for Device 2.

#### Results and Discussion

To prove the validity of the extraction criteria, the extracted experimental parameters, i.e.,  $Q_{it\_exp}$ ,  $C_{it\_exp}$ ,  $\phi_{s\_exp}$ , and  $C_{tot\_exp}$  are compared with the respective calculated, i.e.,  $Q_{it\_calc}$ ,  $C_{it\_calc}$ ,  $\phi_{s\_calc}$ , and  $C_{tot\_calc}$  parameters obtained using the extracted  $D_{it}$  distribution, as shown in the following.

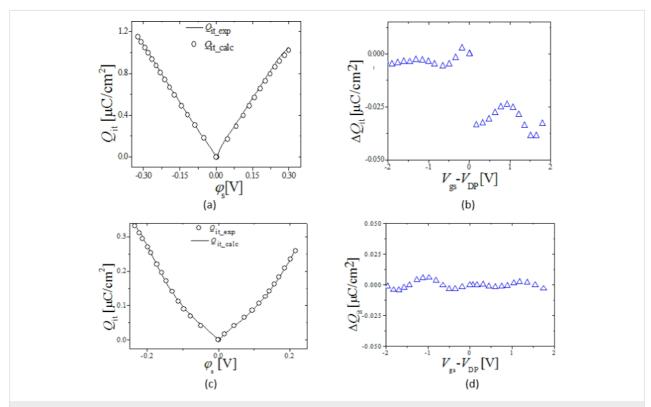

Figure 5a and 5b compare for Device 1 and 2, respectively, the extracted  $Q_{it\_exp}$  from Equation 7 (symbols) as a function of  $\varphi_{s\_exp}$  with the self-consistently calculated  $Q_{it\_calc}$  as a function of  $\varphi_{s\_exp}$  calc.  $Q_{it\_exp}$ , and  $Q_{it\_calc}$  are in reasonable agreement

as shown by Figure 5b and 5d which show the difference in  $Q_{it\_calc}$  and  $Q_{it\_exp}$  as a function of  $V_{gs}$ , for Device 1 and 2, respectively.

Device 2

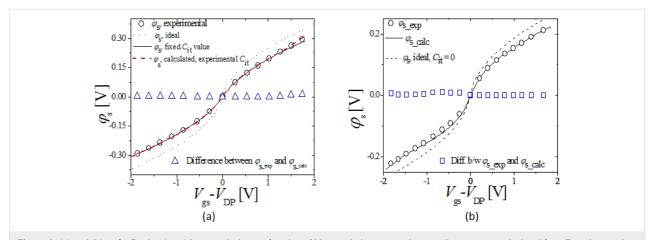

Figure 6a and 6b show for Device 1 and 2, respectively, the extracted  $\phi_{s\_exp}$  (symbols) as a function of  $V_{gs} - V_{DP}$  compared with  $\phi_{s\_calc}$  (solid line) as a function of  $V_{gs} - V_{DP}$ ;  $\phi_{s\_exp}$  is in excellent agreement with  $\phi_{s\_calc}$ .

Also shown is  $\varphi_s$ -ideal, calculated from Equation 4 with  $C_{it}=0$  (dashed line). The surface potential calculated with no  $C_{it}=0$  compared with the surface potential calculated considering  $C_{it}$  clearly indicates that with no  $C_{it}$  included in the surface potential calculation the result will be an erroneously calculated surface potential. Such an erroneous surface potential if used in surface potential based drain current models will lead to unrealistic prediction of device current. Blue symbols in Figure 6a and 6b show the difference in  $\varphi_{s\_exp}$  and  $\varphi_{s\_calc}$ . As the graph shows, the difference between the two is minimal. The model ensures accurate, realistic calculation of device surface potential by taking into account degradation caused by trap states. This feature could be used to develop more realistic drain current models.

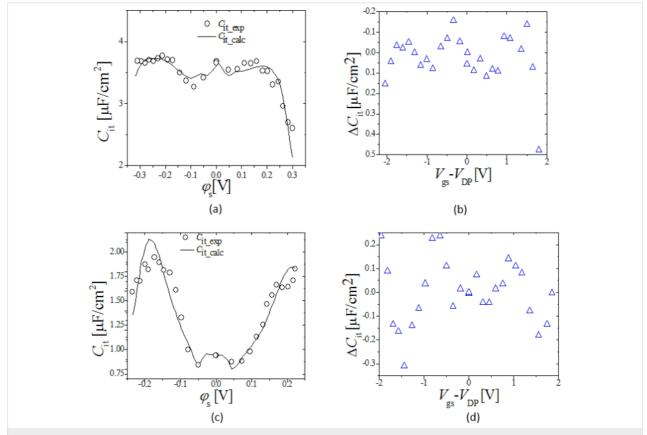

Figure 7a and 7b show for Device 1 and 2 respectively, the extracted  $C_{\rm it\_exp}$  (symbols) from Equation 6, as a function of  $\phi_{\rm s\_exp}$  compared with the  $C_{\rm it\_calc}$  (solid line), as a function of  $\phi_{\rm s\_calc}$ ;  $C_{\rm it\_exp}$  is in reasonable agreement with  $C_{\rm it\_calc}$ . Figure 7b and 7d show difference in  $C_{\rm it\_exp}$  and  $C_{\rm it\_calc}$  as a function of  $V_{\rm gs}$ . The error in  $C_{\rm it\_calc}$  although, higher than  $Q_{\rm it\_calc}$  is still negligible. This is proven when we substitute  $C_{\rm it\_calc}$  in Equation 4 to calculate  $\phi_{\rm s\_calc}$  (when self-consistency is obtained),  $\phi_{\rm s\_calc}$  matches very well with  $\phi_{\rm s\_exp}$  as shown earlier in Figure 6.

Figure 5: (a) and (c)  $Q_{it}$  for Device 1 and 2 respectively, symbols:  $Q_{it\_exp}$  from Equation 7 as a function of  $\phi_{s\_exp}$ , line:  $Q_{it\_calc}$  calculated from Equation 9–11 as a function of  $\phi_{s\_ealc}$ . Figure 5b and 5d show the difference in  $Q_{it\_exp}$  as a function of  $V_{gs}$  for Device 1 and 2 respectively.

Figure 6: (a) and (b)  $\phi_s$  for Device 1 and 2 respectively as a function of  $V_{gs}$ , symbols: extracted  $\phi_{s\_exp}$ , lines:  $\phi_{s\_calc}$  calculated from Equation 4 using the self-consistently obtained  $C_{it\_calc}/Q_{it\_calc}$  from Equation 8–11, dashed lines;  $\phi_{s\_calc}$ -ideal from Equation 4 with  $C_{it}$  = 0. Blue symbols show the difference in  $\phi_{s\_calc}$  and  $\phi_{s\_exp}$ .

Figure 7: (a) and (c).  $C_{it}$  for Device 1 and 2 respectively, symbols:  $C_{it\_exp}$  from Equation 6 as a function of  $\phi_{s\_exp}$ , line:  $C_{it\_ealc}$  calculated from Equation 8–11 as a function of  $\phi_{s\_ealc}$ . (b) and (d) show the difference between  $C_{it\_exp}$  and  $C_{it\_exp}$  as a function of  $V_{gs}$  for Device 1, and 2 respectively.

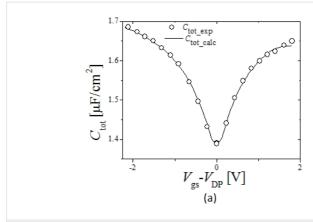

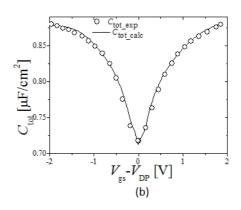

Finally,  $C_{\rm tot\_exp}$  is compared with  $C_{\rm tot\_calc}$  calculated using  $C_{\rm q\_calc}$  from Equation 1, and  $C_{\rm it\_calc}$  obtained above in Equation 2, this is shown in Figure 8a and 8b for Device 1 and 2 respectively;  $C_{\rm tot\_exp}$  (symbols) is in excellent agreement with  $C_{\rm tot\_calc}$  (solid line). All calculated parameters dependent on  $D_{\rm it}$  states, i.e.,  $Q_{\rm it\_calc}$ ,  $C_{\rm it\_calc}$ ,  $\phi_{\rm s\_calc}$  and device  $C_{\rm tot\_calc}$  are in

excellent agreement with the respective extracted experimental parameters, thereby validating the extracted  $D_{it}$  distribution.

It must be mentioned part of this work is based on our earlier work on  $MoS_2$  transistor [14] as briefly mentioned earlier. However, in that work the interface trap density of  $MoS_2$  transity of  $MoS_2$

Figure 8: (a) and (b)  $C_{\text{tot}}$  for Device 1 [7] and 2 [12] respectively, symbols:  $C_{\text{tot\_exp}}$  as a function of  $V_{\text{gs}}$ , lines:  $C_{\text{tot\_calc}}$  from Equation 2 as a function of  $V_{\text{gs}}$ .

sistor was extrated by simply fitting the  $Q_{it}$  parameter in the device's drain current  $(I_{ds})$  model to fit experimental device's  $I_{\rm ds}$  with the calculated one from the model. Next, device's  $\varphi_{\rm s}$ was calculated from the model equation. This  $\phi_s$  was substituted in Equation 9–11 (also used in that work) to fit  $E_{tA/D}$  and  $D_{\rm it}$  values to match  $Q_{\rm it}$  obtained earlier by fitting device's  $I_{\rm ds}$ . This  $D_{it}$  distribution extraction procedure is the same in both works. However, in this work, instead of fitting  $Q_{it}$  in a drain current expression, a thorough analytical framework has been developed, based on fundamental MOGFET device physics, to extract important experimental parameters including  $Q_{it}$ ,  $C_{it}$  and  $\phi_{\rm s}$  data from experimental  $C_{\rm tot}\!\!-\!\!V_{\rm gs}$  data as highlighted in the section "Experimental  $\varphi_s$ ,  $C_{it}$ , and  $Q_{it}$  extraction". Using these experimental parameters as a reference and the framework developed earlier [14,15] an analytical framework was presented to extract the interface trap distribution of MOGFET devices.

To date, to the best of our knowledge this is the only such work in the field. No thorough quantitative, experimental data yet exists on interface trap distribution of graphene transistors. In light of this, this work will be a useful addition to graphene-transistor compact modeling literature.

## Conclusion

In summary, a simple analytic method was introduced to extract the interface trap distribution of MOGFET devices using device's  $C_{\rm tot}$ – $V_{\rm gs}$  data. The model makes use of the basic set of equations used to define device physics of MOGFET devices. Using the procedure mentioned above, interface trap densities of two reference experimental devices were extracted. Device parameters dependent on the extracted interface distribution including the calculated surface potential, interface trap charge, interface trap capacitance and total capacitance matched very well with the respective extracted experimental device parame-

ters. The model enables calculation of device surface potential with the adverse effect of trap charge on device surface potential included. This capability could further be explored in surface potential based MOGFET  $I_{\rm ds}$  models to help predict MOGFET  $I_{\rm ds}$ – $V_{\rm gs}$  performance more accurately by including the effect of interface trap charge on device surface potential.

# Acknowledgements

The authors acknowledge the financial support from UTM GUP Research Grant (Vote no.: Q.J130000.2523.14H27) and Post-doctoral Research University Grant Scheme (Vote no.: Q.J130000.21A2.01E33). MLPT acknowledges the support of the UTM Research Management Centre (RMC) for providing an excellent environment which allowed his result-oriented team to deliver results of high standards worthy of consideration by the industry.

#### References

- Schwierz, F. Nat. Nanotechnol. 2010, 5, 487–496. doi:10.1038/nnano.2010.89

- Lee, Y. G.; Kang, C. G.; Jung, U. J.; Kim, J. J.; Hwang, H. J.; Chung, H.-J.; Seo, S.; Choi, R.; Lee, B. H. Appl. Phys. Lett. 2011, 98, 183508. doi:10.1063/1.3588033

- Lemme, M. C.; Echtermeyer, T. J.; Baus, M.; Kurz, H. *IEEE Electron Device Lett.* 2007, 28, 282–284. doi:10.1109/LED.2007.891668

- Meric, I.; Han, M. Y.; Young, A. F.; Ozyilmaz, B.; Kim, P.; Shepard, K. L. Nat. Nanotechnol. 2008, 3, 654–659. doi:10.1038/nnano.2008.268

- Jimenez, D.; Moldovan, O. IEEE Trans. Electron Devices 2011, 58, 4049–4052. doi:10.1109/TED.2011.2163517

- Zebrev, G. I. Graphene Field Effect Transistors: Diffusion-Drift Theory. In *Physics and Applications of Graphene – Theory*; Mikhailov, S., Ed.; InTech: Rijeka, Croatia, 2011; pp 480–486. doi:10.5772/14211

- Han, S.-J.; Reddy, D.; Carpenter, G. D.; Franklin, A. D.; Jenkins, K. A. ACS Nano 2012, 6, 5220–5226. doi:10.1021/nn300978c

- Ebrish, M. A.; Deen, D. A.; Koester, S. J. Border trap characterization in metal-oxide-graphene capacitors with HfO2 dielectrics. In 71st Annual Device Research Conference (DRC), June 23–26, 2013; IEEE Publishing: Hoboken, NJ, U.S.A., 2013; pp 37–38. doi:10.1109/DRC.2013.6633783

- Akinwande, D. S. P. W. D. Cambridge University Press: Cambridge, United Kingdom, 2011.

- Xu, H.; Zhang, Z.; Xu, H.; Wang, Z.; Wang, S.; Peng, L.-M. ACS Nano 2011, 5, 5031–5037. doi:10.1021/nn201115p

- Zhu, J.; Jhaveri, R.; Woo, J. C. S. Appl. Phys. Lett. 2010, 96, 193503. doi:10.1063/1.3428785

- Nagashio, K.; Nishimura, T.; Toriumi, A. Appl. Phys. Lett. 2013, 102, 173507. doi:10.1063/1.4804430

- Xu, H.; Zhang, Z.; Wang, Z.; Wang, S.; Liang, X.; Peng, L.-M. ACS Nano 2011, 5, 2340–2347. doi:10.1021/nn200026e

- 14. Najam, F.; Tan, M. L. P.; Ismail, R.; Yu, Y. S. Semicond. Sci. Technol. **2015**, *30*, 075010. doi:10.1088/0268-1242/30/7/075010

- Najam, F.; Yu, Y. S.; Cho, K. H.; Yeo, K. H.; Kim, D.-W.; Hwang, J. S.;

Kim, S.; Hwang, S. W. IEEE Trans. Electron Devices 2013, 60, 2457–2463. doi:10.1109/TED.2013.2268193

### License and Terms

This is an Open Access article under the terms of the Creative Commons Attribution License (<a href="http://creativecommons.org/licenses/by/4.0">http://creativecommons.org/licenses/by/4.0</a>), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

The license is subject to the *Beilstein Journal of Nanotechnology* terms and conditions: (http://www.beilstein-journals.org/bjnano)

The definitive version of this article is the electronic one which can be found at: doi:10.3762/bjnano.7.128