# Metrology and technology computer aided design for the sub-10 nm technology node

Edited by Pierre Eyben, Ray Duffy, Narciso Gambacorti and Enrico Napolitani

#### **Imprint**

Beilstein Journal of Nanotechnology www.bjnano.org ISSN 2190-4286 Email: journals-support@beilstein-institut.de

The *Beilstein Journal of Nanotechnology* is published by the Beilstein-Institut zur Förderung der Chemischen Wissenschaften.

Beilstein-Institut zur Förderung der Chemischen Wissenschaften Trakehner Straße 7–9 60487 Frankfurt am Main Germany www.beilstein-institut.de The copyright to this document as a whole, which is published in the *Beilstein Journal of Nanotechnology*, is held by the Beilstein-Institut zur Förderung der Chemischen Wissenschaften. The copyright to the individual articles in this document is held by the respective authors, subject to a Creative Commons Attribution license.

# Absence of free carriers in silicon nanocrystals grown from phosphorus- and boron-doped silicon-rich oxide and oxynitride

Daniel Hiller<sup>\*1,2</sup>, Julian López-Vidrier<sup>2</sup>, Keita Nomoto<sup>3</sup>, Michael Wahl<sup>4</sup>, Wolfgang Bock<sup>4</sup>, Tomáš Chlouba<sup>5</sup>, František Trojánek<sup>5</sup>, Sebastian Gutsch<sup>2</sup>, Margit Zacharias<sup>2</sup>, Dirk König<sup>6</sup>, Petr Malý<sup>5</sup> and Michael Kopnarski<sup>4</sup>

#### Full Research Paper

Address:

<sup>1</sup>Research School of Engineering, Australian National University (ANU), Canberra, Australia, <sup>2</sup>Laboratory for Nanotechnology, Department of Microsystems Engineering (IMTEK), University of Freiburg, Germany, <sup>3</sup>The University of Sydney, Faculty of Engineering and Information Technologies, School of Aerospace, Mechanical and Mechatronic Engineering, Sydney, Australia, <sup>4</sup>Institute for Surface and Thin Film Analysis GmbH (IFOS), Kaiserslautern, Germany, <sup>5</sup>Department of Chemical Physics and Optics, Charles University, Prague, Czech Republic and <sup>6</sup>Integrated Materials Design Centre (IMDC), University of New South Wales (UNSW), Sydney, Australia

Email:

Daniel Hiller\* - daniel.hiller@anu.edu.au

\* Corresponding author

Keywords:

atom probe tomography; doping; photoluminescence; silicon nanocrystals; transient transmission

Beilstein J. Nanotechnol. **2018**, 9, 1501–1511. doi:10.3762/bjnano.9.141

Received: 01 February 2018 Accepted: 25 April 2018 Published: 18 May 2018

This article is part of the thematic issue "Metrology and technology computer aided design for the sub-10 nm technology node".

Guest Editor: P. Eyben

© 2018 Hiller et al.; licensee Beilstein-Institut. License and terms: see end of document.

#### Abstract

Phosphorus- and boron-doped silicon nanocrystals (Si NCs) embedded in silicon oxide matrix can be fabricated by plasma-enhanced chemical vapour deposition (PECVD). Conventionally, SiH<sub>4</sub> and N<sub>2</sub>O are used as precursor gasses, which inevitably leads to the incorporation of  $\approx$ 10 atom % nitrogen, rendering the matrix a silicon oxynitride. Alternatively, SiH<sub>4</sub> and O<sub>2</sub> can be used, which allows for completely N-free silicon oxide. In this work, we investigate the properties of B- and P-incorporating Si NCs embedded in pure silicon oxide compared to silicon oxynitride by atom probe tomography (APT), low-temperature photoluminescence (PL), transient transmission (TT), and current–voltage (I–V) measurements. The results clearly show that no free carriers, neither from P- nor from B-doping, exist in the Si NCs, although in some configurations charge carriers can be generated by electric field ionization. The absence of free carriers in Si NCs  $\leq$ 5 nm in diameter despite the presence of P- or B-atoms has severe implications for future applications of conventional impurity doping of Si in sub-10 nm technology nodes.

Open Access

#### Introduction

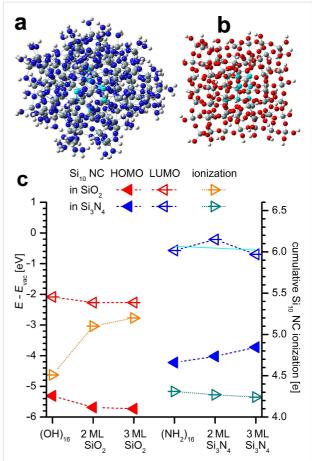

The conductivity type and free carrier concentration of a semiconductor can be controlled via doping. Conventional impurity doping requires the incorporation of a suitable foreign atom on a lattice site and its ionization by thermal energy. Therefore, the energetic position of a dopant in the bandgap has to be close to the respective band edges. For Si, typical dopant ionization energies are in the range of ≈50 meV. If the size of the Si crystal approaches the exciton Bohr-radius, strong quantum confinement sets in and the valence- and conduction band ground state energies shift to lower and higher energies, respectively. As a consequence, the dopant ionization energies increase, which decreases exponentially the free carrier density [1]. If a doped Si-nanovolume is embedded in a matrix of lower permittivity (e.g., a dielectric), the dopant charge is not fully screened in the silicon and a Coulomb interaction with its image charge in the dielectric occurs. Irrespective of quantum confinement, this so-called dielectric confinement increased the dopant ionization energy even further [2]. At the nanoscale, the incorporation of an impurity on a lattice site is also subject to an increased formation energy as compared to the bulk, so that despite of thermal activation via, e.g., a high-temperature annealing process a significant fraction of potential dopants will remain on interstitial sites [3]. The decreasing number of Si-Si bonds per Si NC atom is a crucial point for the increase of dopant formation energies [4]. These factors impede efficient impurity doping of Si nanovolumes and complicate applications of Si NCs in devices based on p-n-junctions such as solar cells or light emitting devices [5,6]. Furthermore, semiconductor device fabrication technology nodes target the sub-10 nm scale in the near future, i.e., length scales where the effects described above will appear.

Si NCs of a few nanometres in diameter (i.e., quantum dots) represent a good model system to study doping at the nanoscale. They can be fabricated by various methods [7-9] and doped either during growth [7] or post-growth [10]. A recent review provides a broad overview of all available techniques and approaches [11]. Here, we focus on the Si NC growth via phase separation of PECVD-deposited, P- or B-doped silicon-rich oxide thin films via annealing at high temperatures. Additionally, we focus on comparatively lowly doped samples (on the order of 0.1-1 atom %) to study the classical electronic doping of Si NCs. In contrast, dopant concentrations up to 60% (also referred to as hyperdoping) were shown to induce localized surface plasmon resonances and metal-like free carrier densities [12-15]. The standard PECVD precursor gasses for silicon oxide are SiH<sub>4</sub> and N<sub>2</sub>O. Since Si-rich oxides have to be grown in O-depletion, some of the N-radicals present in the plasma react with the Si and are subsequently incorporated in the film. The resulting material is inevitably a Si-rich oxynitride (SRON) with in our case  $\approx$ 10 atom % N [16]. Considering some safety issues, the oxidizing PECVD precursor gas can be replaced by O<sub>2</sub>, which allows for N-free Si-rich oxides (SRO) [17]. In both cases, small amounts of PH<sub>3</sub> or B<sub>2</sub>H<sub>6</sub> can be added during deposition to achieve P- or B-doped SRON or SRO, respectively.

In this study, we investigate the structural, optical and electrical properties of P- and B-incorporating Si NCs in both embedding dielectrics. We will show that, despite some minor differences in the four different sample configurations, no free carriers associated to a doping behaviour of P or B are observed.

#### Experimental

Superlattices of SiO2 and SRO, or respectively, SRON were deposited on Si and quartz glass substrates by PECVD using processes described in [16,17]. Small amounts of 1% PH<sub>3</sub>/Ar, or respectively, 10% B<sub>2</sub>H<sub>6</sub>/SiH<sub>4</sub> were added to the Si-rich layers (both SRO and SRON) whereas in all cases the SiO2 barrier layers remained undoped. All samples were annealed for 1 h in ultra-pure N<sub>2</sub> in a quartz tube furnace at 1100 °C (SRO) and 1150 °C (SRON). The thicknesses of the Si-rich oxide layers determine the mean size of the Si NCs to be of approximately the size of the initial layer thickness. Samples dedicated to luminescence and electrical measurements were postannealed in the same furnace in pure H2 gas at 450 °C for 1 h to enable the passivation of dangling bond defects [18]. For electrical measurements, MOS capacitors were processed by thermal evaporation of Al-contacts. Molecular Cs<sup>+</sup> secondary ion mass spectrometry (MCs<sup>+</sup>-SIMS [19]; Cameca IMS-4f) with 3 keV Cs<sup>+</sup> (for SRO:P/B) and 5.5 keV (for SRON:P/B) Cs<sup>+</sup> was used to quantify sample composition including the P- or B-concentration by means of a calibrated standard. APT was measured with a LEAPTM 4000X Si (Cameca) with a pulsed UV laser (355 nm, 100 pJ, 250 kHz), a cooled specimen holder ( $\approx$ 40 K) and a chamber pressure of  $10^{-12}$ – $10^{-11}$  Torr. The atom detection efficiency is 57%. For data reconstruction IVASTM software (version 3.6.6) was used. APT specimen (needleshaped tips attached onto the apex of a Mo support grid) were structured using an Auriga (Zeiss) focused ion beam scanning electron microscope. PL was measured using a LN2-cooled CCD camera attached to a single grating monochromator with excitation of a HeCd laser (325 nm line). Low-temperature PL spectra were measured from 5 to 300 K using a single-window continuous-flow liquid-He cryostat. TT-dynamics were measured in a standard pump and probe configuration by a laser system with 100 fs pulse length and 1 kHz repetition rate (Tsunami, Spitfire, Newport). The fundamental 800 nm output was partly used as a probe and partly frequency doubled to 400 nm and used as a pump. The measurements were done at

room temperature. I-V and I-t was measured under accumulation bias, in dark and at room temperature, with an Agilent B1500A semiconductor device analyser and a Cascade M150 Prober in a shielded dark box.

#### Results and Discussion

#### Dopant concentration and -incorporation

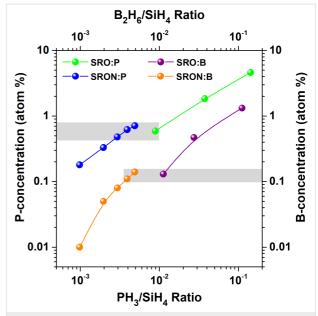

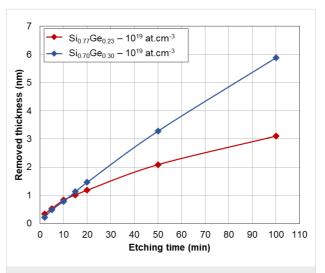

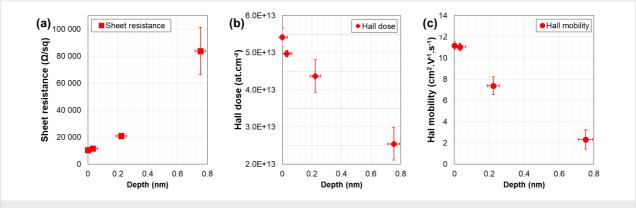

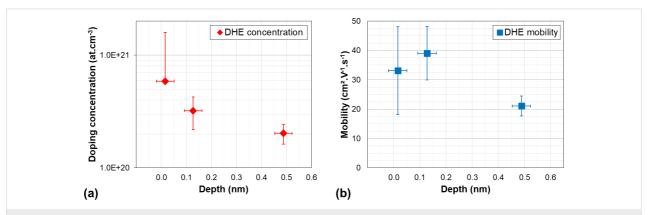

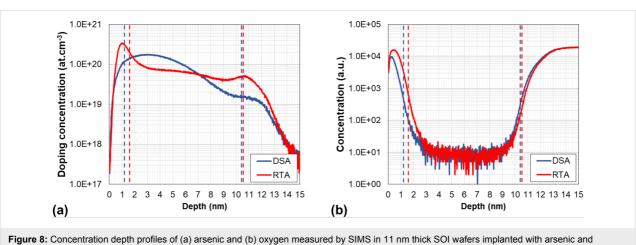

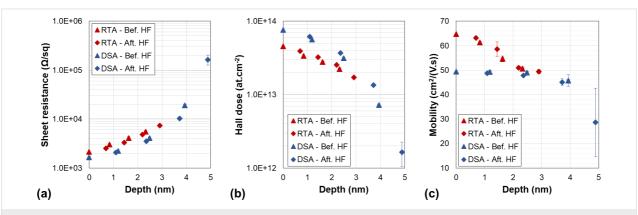

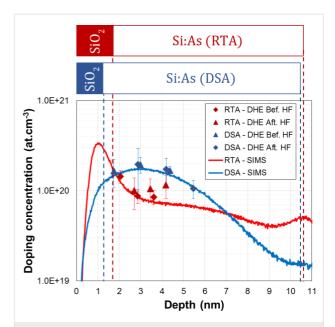

At first, we determine the P-concentration as function of PH<sub>3</sub>flux for SRO and SRON via MCs+-SIMS measurements. For this task, special samples were fabricated consisting of several 50 nm-thick SRO:P and SRON:P layers with different PH<sub>3</sub>fluxes, separated by SiO<sub>2</sub> spacing layers (20 nm and 10 nm thickness, respectively). The SIMS depth profiles for as-deposited SRO:P and SRON:P are shown in Figure S1a and Figure S1b of Supporting Information File 1. It turns out that the P-concentration in SRO:P can be adjusted by the available PH<sub>3</sub>-flux from 0.59-4.61 atom %, while for SRON:P the range is limited to 0.18-0.71 atom %. In Figure S1c and Figure S1d of Supporting Information File 1 the SIMS depth profiles for similarly configured SRO:B and SRON:B layers are shown. Here, the B-concentration is controlled by the B<sub>2</sub>H<sub>6</sub>-flux in the range from 0.13-1.32 atom % for SRO:B and 0.02-0.14 atom % for SRON:B. When plotting the P- and B-concentrations in the Si-rich oxides as function of the flux ratio of PH3 and SiH4 or B<sub>2</sub>H<sub>6</sub> and SiH<sub>4</sub>, respectively, a quasi-linear dependence is found; see Figure 1. Generally, the dopant concentrations in SRON are lower than in SRO, which is caused by the very different precursor gas flows used in the SRON [16] and SRO [17] recipes. Nevertheless, for both dopants there is a concentration overlap region (indicated by grey boxes in Figure 1) for P in the range of  $0.6 \pm 0.1$  atom % and for B in the range of  $0.13 \pm 0.02$  atom %. Any direct comparison between doped SRO and SRON samples should hence be made in that overlap region to allow for equal nominal dopant concentrations. While the dopant-precursor flows are similar for each Si-rich oxide type, the average concentration of dopants is a factor of ≈5 lower for B than P, although the same amount of B2H6 gas contains twice the number of dopant atoms compared to PH<sub>3</sub>. As a consequence, the incorporation efficiency of B in Si-rich oxides is approximately one order of magnitude lower than that of P.

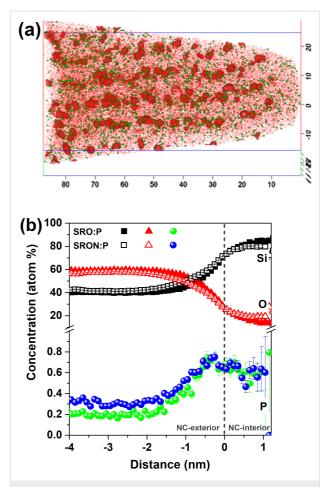

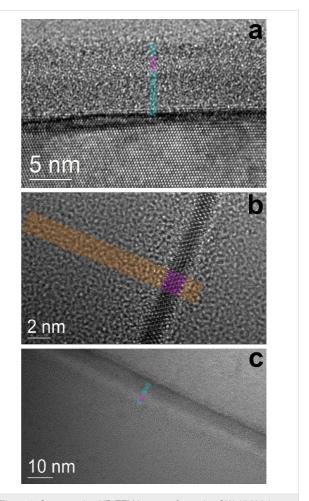

Since SIMS cannot reveal the distribution of the dopants in the heterogeneous sample system of Si NCs and SiO<sub>2</sub> after annealing, atom probe tomography (APT) is used. APT was demonstrated to be a powerful method to reveal structural details of impurity elements in Si NCs [20,21]. In order to determine the incorporation of P-atoms into Si NCs, APT was measured for samples with SRO:P-0.59 atom % (for an image of a typical 3D-reconstruction see Figure 2a) and SRON:P-0.71 atom %. The mass spectra can be found in Figure S2 of

**Figure 1:** P- and B-concentrations as measured by MCs<sup>+</sup>-SIMS as function of PH $_3$  to SiH $_4$  gas flow ratio, or respectively, as function of B $_2$ H $_6$  to SiH $_4$  gas flow ratio for both SRO and SRON PECVD-recipes. The lines are just a guide to the eye to indicate the nearly linear dependences. The grey boxes indicate the concentration overlap regions for P- and B-doped SRO and SRON materials, respectively.

Supporting Information File 1. For reference and to exclude critical mass spectra peak overlaps of, e.g.,  ${}^{31}P^{+}$ ,  ${}^{30}Si^{16}O_{2}^{2+}$ , and 30Si1H+ an additional P-free sample was measured and no other signals influencing the ascription to P were found. Furthermore, the signals at 14 Da (Dalton, i.e., the unified atomic mass unit) and 28 Da indicate a very small influence of N on the mass spectra, which is consistent with its rather high ionization energy. Signals of <sup>14</sup>N<sup>2+</sup> at 7 Da and <sup>14</sup>N<sub>3</sub><sup>+</sup> at 42 Da in the mass spectra are assigned to N-ion peaks but their contribution is too small to quantify the amount of N. The determination of P-ions in the mass spectra in this study was carried out without further data correction (e.g., for delayed evaporation events, so-called thermal tails). Still, the method to analyse the data of both SRON and SRO samples is the same, thus, P-concentrations are directly comparable to each other. In Figure 2b the proxigram analyses (proximity histograms) [22] of all detected NCs in the respective samples are shown. As selected in previous works, the Si NCs were created by 70 atom % Si iso-concentration surfaces [23]. A voxel size of 0.5 nm and a delocalization value of (x, y, z) = (1 nm, 1 nm, 1.5 nm) were used [24]. The bin size of the proxigram was set at 0.1 nm. Note that these parameters do not change the trend of the composition profiles of both samples. On first sight, no significant differences in the distribution of P-atoms in the NC-interior, at the Si/SiO<sub>2</sub> interface, and in the SiO<sub>2</sub> matrix are found. Especially the interior of the Si NCs and the near-interface region of the SiO2 have almost identical P-concentrations of

≈0.5–0.7 atom %, while in the N-free SiO<sub>2</sub> matrix apparently less P is dissolved (≈0.2 atom %) compared to the oxynitride matrix ( $\approx 0.3$  atom %). However, given the 20% (relative) higher initial P-concentration in SRON:P compared to SRO:P and a measurement uncertainty in the range of 0.1 atom %, this difference might be negligible. The overall P-distribution corresponds very well to previously observed trends for P in Si NCs [23-26]. We note that the  $\approx$ 20% O-concentration in the NC-interior is an artefact from local magnification effects (LME) [27,28] which is generally observed in this material system [24-26,29,30]. Inevitably, this artefact also influences the exact values of the P-concentration, but since both samples are subject to the same LME the comparison discussed above is not influenced. Besides LME there are also other factors influencing the precision and resolution of APT such as inhomogeneous tip shape evolution during the measurement [31], delayed dissociation of molecules during the flight [32], and associated problems with the detection of neutral fragments [33]. Still, APT provides unique and very useful data inaccessible by any other method.

In Figure S3a of Supporting Information File 1 the NC-size distribution as derived from APT using iso-concentration surfaces of ≥70 atom % Si is plotted as well as the relative frequency of the number of P-atoms per NC. The number of P-atoms incorporated per NC and the P/Si-ratio, both as function of NC-volume, are shown in Figure S3b of Supporting Information File 1. While details of this data set are discussed in Supporting Information File 1, it can be readily concluded that the P-distribution and NC-incorporation is very similar for both SRO:P and SRON:P. Therefore, the presence of N in the oxynitride matrix has apparently no influence on the structural properties of P-doped NC-samples.

The SRO:B material has already been APT-analysed in [30] with the result that B is generally less likely to be incorporated deep in the NC core but more near the inner surface (in agreement with former theoretical [34,35] and experimental [26] evidence). Due to the maximum B-concentration in SRON:B of only 0.14 atom %, a statistically meaningful APT-analysis cannot be achieved. However, the absence of any significant differences between SRON:P and SRO:P suggests that the nitrogen in the oxynitride matrix will not have a notable influence on the B-distribution when SRON:B and SRO:B are compared.

## Photoluminescence and transient transmission

Due to quantum confinement effects the ground state energy of Si NCs increases and the k-space overlap of electron and hole wave functions are significantly enhanced (Heisenberg's uncer-

Figure 2: (a) Atom probe tomography reconstruction of P-doped Si nanocrystals (red iso-surfaces with ≥70 atom % Si) in N-free SiO₂ matrix (P-atoms: green; Si-atoms: red; all axes in nm). (b) Proxigram analysis of Si NCs grown from SRO:P (0.59 atom %) and SRON:P (0.71 atom %). The local P-concentrations are depicted in green for SRO:P and blue for SRON:P. Positive distances refer to the inner NC-volume, negative distances to the surrounding matrix.

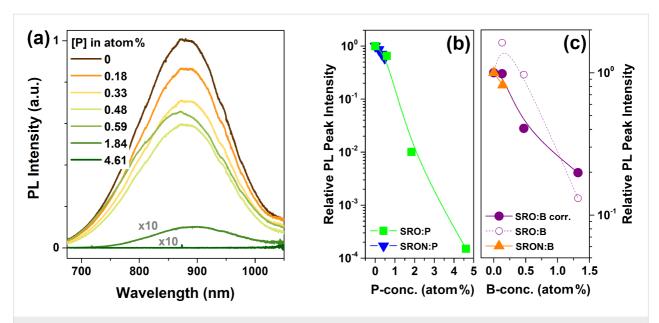

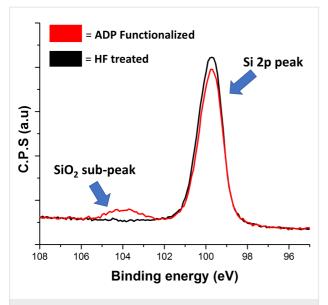

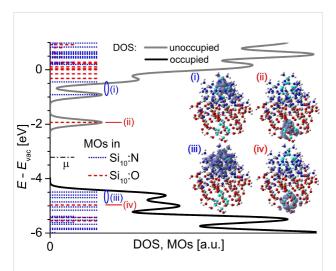

tainty principle). Therefore, excitons formed in Si NCs are subject to significantly higher radiative recombination probabilities, allowing the luminescence quantum yield to reach ≈30% [36,37], or even  $\approx$ 60% for organically-capped NCs [38]. In the presence of a third charge carrier (a free electron from an ionized P-donor or a hole from an ionized B-acceptor) radiative recombination is very unlikely, since ultra-fast non-radiative Auger recombination will prevail [7]. On the other hand, the observation of PL quenching alone cannot prove the presence of free carriers since also dopant-induced defects can be involved [29,30,39-41]. In Figure 3a, the dependence of the PL spectra on the P-concentration in SRO:P and SRON:P is demonstrated. Here, all samples are H<sub>2</sub>-passivated and hence only the PL-quenching effect of P-incorporation is visible, not the PL-enhancement often observed for low P-concentrations and associated to dangling bond passivation by P [42]. Up to the level of ≈0.6 atom % P the PL intensity drops by less than 40%

Figure 3: (a) Room temperature photoluminescence spectra of P-incorporating Si NCs in SRON (0–0.48 atom %) and SRO (0.59–4.61 atom %). The spectra of the two highest P-concentrations are multiplied by a factor of 10 for better visibility. (b) and (c) logarithmic PL peak intensity as function of P-concentration, or respectively B-concentration, in SRO and SRON, normalized to the respective dopant-free samples. For SRO:B-samples the PL-intensities are corrected for the excess-Si content (open purple circles show the raw data). Lines are just a guide to the eye. For both dopants it is obvious that significant PL-quenching requires P-/B-concentrations >1 atom %.

without any significant peak shift. According to the APT data shown above and in Supporting Information File 1 only the smallest NCs of each sample remain rather P-free and therefore potentially PL-active, which would implicate a strong PL blueshift, if Auger quenching by P-donors is considered. From Figure 3a and 3b, however, it is obvious that neither a spectral shift nor an efficient PL-quenching by P-incorporation takes place. In contrast, the PL remains very intense up to a P-concentration in SRO beyond >1 atom % P, i.e., vastly exceeding the solubility limit of P in Si. An almost complete suppression of PL occurs only for samples with 4.61 atom % P. Within the concept of PL-quenching by free-carriers induced by P-atoms in the Si NCs, it remains dubious why concentrations of several atom-percent should be required although APT detects in the majority of NCs already one or several P-atoms for samples with 0.6-0.7 atom % P. It appears more consistent with the available data that P-induced defects (e.g., from interstitial P in the Si NCs or SiO<sub>x</sub>:P-related states at the surface) cause the PL quenching, as supported by density functional theory (DFT) calculations [29,41]. In that context, it is also likely that for samples with >1 atom % P the P-concentration peak found at the Si/SiO<sub>2</sub> interface (cf. Figure 2b) reaches a level where a highly enriched P-shell forms on the NC-surface that enables efficient formation of non-radiative defect states.

For boron, strong PL-quenching is also not observed before the B-concentrations exceed >1 atom %, as shown in Figure 3c, and the same argumentation holds true for B-induced defects with

states in the fundamental gap of Si NCs, as determined by DFT [30]. The as-measured PL peak intensity of the SRO:B sample set (open purple circles) is unfortunately obscured by variations in the initial excess-Si content (cf. Figure S1c of Supporting Information File 1), which directly influences the NC-density in those samples. Hence, the data set is corrected by the excess-Si content as measured by MCs<sup>+</sup>-SIMS (filled purple circles in Figure 3c; for details see caption of Figure S1 of Supporting Information File 1).

We note that the overall PL-quenching behaviour of Si NCs in doped SRO and SRON is similar. Hence, the presence of nitrogen in the matrix does not have a major impact on the formation of B- or P-induced centres that quench the PL.

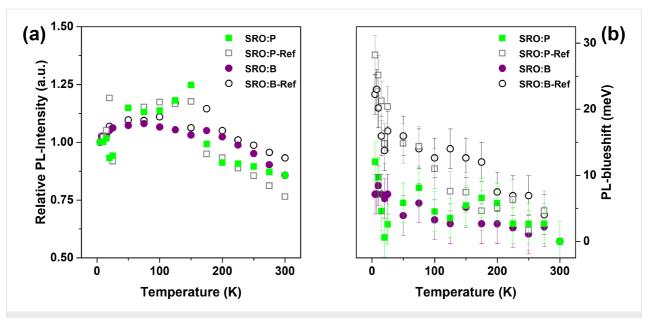

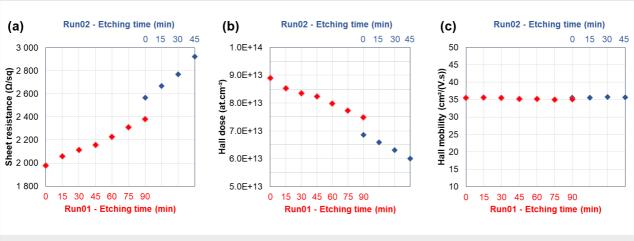

Electronic doping, i.e., the generation of free carriers from dopants on substitutional lattice sites, requires thermal ionization, typically provided by the thermal energy at room temperature. Ignoring all the evidence of a defect-related PL-quenching of Si NCs containing P- or B-atoms, we would anticipate from low-temperature PL measurements of successfully, electronically doped Si NCs: (i) an increase in the PL-intensity as soon as free carriers are frozen out, accompanied by (ii) a spectral redshift due to the circumstance that within the NC-size ensemble the largest NCs are more easily doped than the smaller NCs, and (iii) significant differences in the PL peak behaviour when compared to undoped reference samples. In Figure 4, the T-dependent PL-peak analyses of spectra measured at very low exci-

Figure 4: Low-temperature PL data of samples with 5 nm SRO and 0.59 atom % P (SRO:P), 0.47 atom % B (SRO:B) and their respective intrinsic references (SRO:P-Ref, SRO:B-Ref). (a) Relative PL-intensities with respect to the measured value at 5 K of each sample, i.e., the lowest temperature where all potential dopant-induced carriers are completely frozen out. There is hardly any difference visible in the PL-intensity over temperature between doped and undoped samples. (b) PL peak shift with reference to the peak at 300 K, i.e., where ionized donors and acceptors would quench predominantly the largest NCs in each sample. A slight PL-blueshift is observed, not a redshift as expected from NC-doping.

tation fluxes of  $\approx$ 0.4 mW/cm² (to prevent over-excitation artefacts [43]) are presented. The spectra themselves can be found in Figure S4 of Supporting Information File 1. Figure 4a shows the relative PL-intensity as function of sample temperature (T) with respect to the intensity at 5 K, where all free carriers from potential dopants would be completely frozen out. The intensity trends follow roughly the low-excitation measurements shown in [44]. For approx. T > 150 K the intensity drops below unity due to the thermal activation of non-radiative recombination channels [36,44]. The relative PL-intensities of all samples with respect to their 5 K values end up in the same range of values at room temperature. Hence, a freeze-out effect of dopant-induced free carriers that quench the PL is not observed in accordance with dopant-induced defect states deep within the fundamental gap of the NCs.

Figure 4b plots the PL peak shift with reference to 300 K, i.e., where a maximum of dopant-induced free carriers would quench the PL, which would preferentially affect the larger NCs with least confinement energy. Instead of a PL redshift expected for doped NCs with decreasing T, we observe a small blueshift related to the thermal contraction of the lattice and reduced electron–phonon interaction, which typically saturates around 100–200 K for lowly excited samples [43]. To add, the blueshift of the reference samples is slightly more pronounced for T < 150 K than that of the doped samples. The increase for  $T \le 25$  K is most likely an artefact from overexcitation [43] despite the very low laser intensity. The reason for using two

nominally identical reference samples (both are undoped SRO) in PL is due to the different number of NC-layers in the superlattice (10 for SRO:P and 20 for SRO:B). Any differences between the reference samples might therefore be interpreted as the scattering amplitude between different samples.

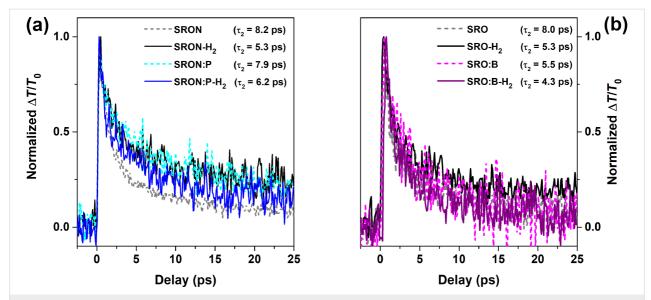

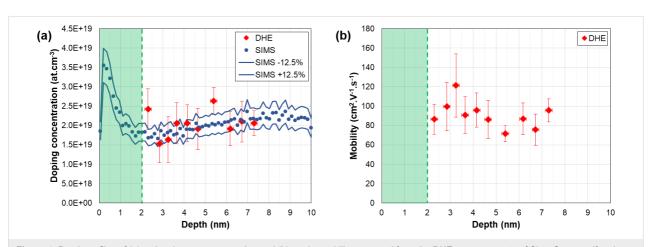

In Figure 5 we report the transient transmission dynamics of samples with 4.5 nm Si NCs made of (a) SRON:P with 0.71 atom % P and (b) SRO:B with 1.32 atom % B, i.e., samples with substantial incorporation of dopant atoms and significant PL quenching. For this measurement the excitation pump pulse wavelength was 400 nm (efficiently absorbed by the NCs) and the probe pulse wavelength was 800 nm, which is hardly absorbed by the NCs. However, if free carriers are present in the NCs, whether from optical excitation or from doping, the probe light is absorbed. The transmission of the sample at the probe wavelength in the unexcited state is measured as  $T_0$  and the transmission as function of delay time between pump and probe (in steps of  $\approx 100$  fs) is plotted as

$$\frac{T - T_0}{T_0}$$

The pump flux is chosen to generate only a few excitons per NC [45]. Specifically, 2.3 mJ/cm<sup>2</sup> (SRON) and 3.4 mJ/cm<sup>2</sup> (SRO) were used, which correspond to the excitation regime with normal Auger recombination of excitons, excluding bimolecular recombination [46]. If an additional free carrier (electron

Figure 5: Transient transmission (TT) dynamics from pump-probe measurements at room temperature of  $\approx$ 4.5 nm Si NCs from (a) SRON:P and P-free SRON and (b) SRO:B and respective B-free SRO. All samples are measured before and after H<sub>2</sub>-passivation. The curves are normalized for better comparability of the decay dynamics (although no significant or even doping-related differences exist in the initial signal intensity of the samples). The time constants of the component  $\tau_2$  of the two-exponential fits (not shown for clarity) are given in the figure. The presence of P- or B-atoms in the NCs does not increase the speed of carrier recombination, as would be expected from the presence of dopant-induced free carriers.

from P-donor or hole from B-acceptor) would be present in a Si NC, the generated exciton(s) could efficiently and quickly recombine with the unpaired charge carrier via an Auger process. This would substantially accelerate the reduction of the total carrier density and a doped sample would become transparent in shorter time as compared to an intrinsic sample. It is obvious from Figure 5a and 5b that neither for SRON:P nor for SRO:B accelerated TT-dynamics exist. When fitting the curves, best results are obtained for a two-exponential fit

$$\frac{\Delta T}{T_0} \sim e^{-t/\tau_1} + e^{-t/\tau_2},$$

where the fast component  $\tau_1 \approx 0.5 \dots 1.5$  ps for all samples is attributed to ultrafast carrier trapping and thermalization events. The long component  $\tau_2$  is associated with the actual Auger recombination of excitons and ranges from 5 to 8 ps without differences between doped or undoped samples. We conclude that no measurable initial carrier densities exist at room temperatures in P- or B-doped Si NCs in silicon oxide matrix.

The TT-results are presented for both H<sub>2</sub>-passivated and unpassivated states without distinctive differences, but one remark concerning the interaction of Si-doping and hydrogen shall be made: While P in the Si NC system is known to passivate dangling bonds (DBs) at the Si/SiO<sub>2</sub> interface [7,42] similar to a post-annealing in H<sub>2</sub>, hydrogen treatments have also been shown to deactivate P-donors and B-acceptors in heavily doped Si nanowires [47] and in the bulk [48-50]. However, this type of

dopant passivation solely relies on very reactive atomic hydrogen (rather than molecular  $H_2$  gas) and requires much lower temperatures of  $100\text{--}150\,^{\circ}\text{C}$  to be efficient. When considering  $H_2$  as used in our work, the effective (endothermic) dissociation enthalpy of the reactions 2 P-DB +  $H_2 \rightarrow 2$  P-H and 2 Si-DB +  $H_2 \rightarrow 2$  Si-H yield ca. 0.05 eV and ca. 0.09 eV per DB passivation, respectively [51]. This finding renders the P-H bond breakage to occur at significantly lower temperatures as used at  $H_2$  anneals to passivate Si-DBs (450–500 °C).

Such a H-passivation mechanism of dopants requires their substitutional incorporation, which occurs apparently only in very small fractions for dopants in Si NCs (see section Electrical properties below). Therefore, neither from experimental evidence nor from fundamental considerations, it can be argued that the doping effect of P or B in Si NCs is obscured by H<sub>2</sub>-passivation. In contrast, the passivation of DB-defects at the Si/SiO<sub>2</sub> interface often improves the interpretability of the measured data.

#### Electrical properties

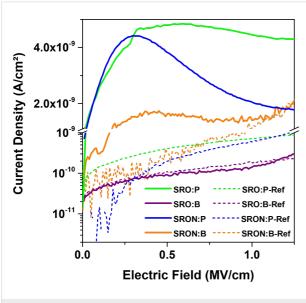

If free charge carriers would be present in the Si NCs, or if they are generated via ionization by an external electrical field, it is possible to detect their presence by *I–V* measurements on MOS-capacitors with additional injection barriers [52,53]. Respective samples (injection-blocking MOS-capacitors) were fabricated with 10 nm-thick SiO<sub>2</sub> buffer and capping layers to prevent low-field injection of carriers from either substrate or gate, so that only transient displacement currents are measured. The cur-

rent density over electric field (J-E) curves of B- or P-incorporating SRO and SRON samples, together with dopant-free reference samples, are depicted in Figure 6. None of the reference samples (dashed lines) shows a current peak in the low E-field regime, which excludes significant contributions to the displacement current by undoped Si NCs or their host matrices (pure oxide vs oxynitride). The *J*-curves of the P-incorporating NCs show a broad peak at ≈0.5 MV/cm for SRO:P and a sharper peak at ≈0.3 MV/cm for SRON:P. The peak character for SRO:P is less clearly expressed. Whereas the rising shoulders of both J-peaks are quite similar, only for the SRON:P sample the current density decreases behind the peak with a comparable slope but remains on a plateau for SRO:P. The origin of the *J*-signal is the ionization of substitutional P-atoms in Si NCs and the subsequent accumulation of the "free" charge carriers under the gate blocking oxide (cf. [29] and [52] for details). Following the calculations therein, we can estimate the P-ionization energy of the J-peak (or respectively the beginning of the J-plateau) to ≈200 meV, in accordance with literature values on ionization energies of nano-sized Si [54,55]. For SRO:P the J-plateau indicates a broader distribution of P-ionization energies towards even larger values.

**Figure 6:** *J–E* data of injection-blocking MOS-capacitors with P- or B-incorporating Si NCs in SRO and SRON and their directly corresponding references (SRO:P with 0.59 atom %, SRON:P with 0.48 atom %, SRO:B with 1.32 atom %, SRON:B with 0.14 atom %).

The comparison between SRO:B and SRON:B is even more surprising: While Si NCs from SRO:B do not show a J-peak but rather identical I-V behaviour as the respective reference, the SRON:B sample shows a weak plateau-like peak at  $\approx 0.4$  MV/cm. It is emphasized that the J-peak is found in the maximum possible B-doped SRON sample, but not in the max-

doped SRO:B sample, despite an almost one order of magnitude higher B-concentration in the latter. Hence, B-doped Si NCs may be field-ionized in SRON, in contrast to our previous report on SRO [30] and in accordance with [53]. The hole-tunnelling properties of the matrix seem to determine the visibility of this effect and oxynitride seems to allow for a better hole transport (maybe assisted by N-related states), while N-free pure oxide apparently camouflages the field-ionization of B in SRO:B. In the case of electrons from field-ionized P-donors the situation is less critical since the conduction band offset of Si NCs and SiO<sub>2</sub> is only about half that of the valence band offset [56].

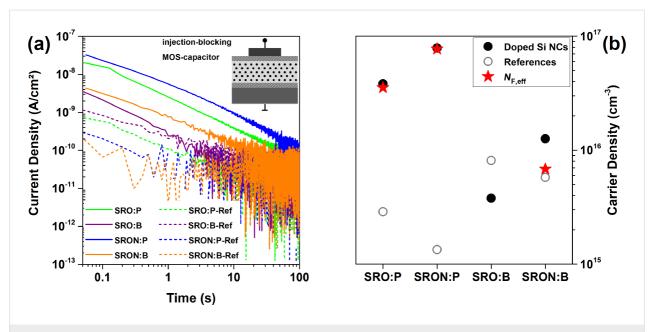

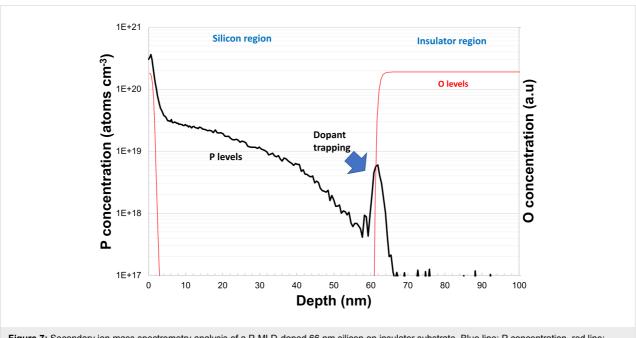

Figure 7a shows I-t-transients of the injection-blocked MOScapacitors (the inset depicts a schematic cross-section) measured at 0.2 MV/cm, i.e., at the onset of the J-peak/plateau (if present). As expected from the device geometry, all transient displacement currents reach the noise level at the minimum detectable limit (sub-pA range), which marks the end of the measurements. Whereas the fast drop of J of the reference samples within the first seconds of the measurement is attributed to dielectric relaxation, the P-doped Si NC samples clearly show mobile charge redistributions on a longer timescale. For the B-doped Si NCs the situation is less clear, since the noise level is reached earlier. A likely cause for this behaviour might be a lower density of redistributable charge. With the exception of SRO:B samples, there is also a 1–2 orders of magnitude higher J-level throughout a major part of the transient period between the doped samples and their respective references. By integrating the measured current over time, the corresponding total charge, generated by field ionization of dopants on Si-lattice sites in the NCs, can be estimated [52]. The free carrier densities of all samples at 0.2 MV/cm are shown in Figure 7b. Values of  $(4 \pm 3) \times 10^{15} \text{ cm}^{-3}$  were obtained for the reference samples (grey open circles); we note that these values are strongly influenced by dielectric relaxation. From the doped samples (black filled circles) only SRO:B has a similar value (being slightly below its reference). All other doped NC-samples have free carrier concentrations in the  $10^{16} \,\mathrm{cm}^{-3}$  range. In order to exclude a contribution to the free carrier values from the dielectric relaxation, we subtract the reference-values to obtain the effective free carrier density ( $N_{\rm F,eff}$ , red spheres in Figure 7b). It is obvious that P dominates over B and SRON over SRO: Sample SRON:P has about twice the integral charge than SRO:P and SRON:B is an order of magnitude lower than SRON:P. In this context, point out that SRON:B has a B-concentration that is just 30% of the P-concentration in SRON:P. Although the initial dopant concentration in the Si-rich oxide is not the figure of merit but the substitutional incorporation in the NCs, these results still indicate that B-doping is less efficient than P-doping. This is underlined by

Figure 7: (a) J–t transients of the same MOS-capacitors as in the previous figure measured at E = 0.2 MV/cm. The inset shows a schematic cross-section of the device under test. (b) Free carrier density from field ionization of substitutional dopants derived from integrating transient current over time. For effective free carrier values ( $N_{F,eff}$ ) the values of the dopant-free references values are subtracted from the values of the doped Si NC samples.

the electrical properties of the SRO:B samples, which do not even have a positive effective free carrier density. Here, the very small effective free carrier density of SRO:B is exceeded by the carrier density of SRO:B-Ref, which might originate from the slightly different NC-density caused by the B-dependent Si-content (cf. Figure S1, Supporting Information File 1). We note that for SRON:P a field ionization doping efficiency of  $\approx\!\!4\%$  was derived by dividing  $N_{F,eff}$  with the number of P-atoms in the NCs measured by APT [29], which allows to estimate for Si NCs from SRO:P a field ionization doping efficiency of  $\approx\!\!2\%$ , whereas for SRON:B in absence of measurable APT results no efficiency can be estimated.

#### Conclusion

Comparing oxynitride and N-free oxide as matrix for P- or B-incorporating Si NCs, no significant differences were observed structurally (SIMS, APT) or optically (PL, TT). Electrically (*I–V*, *I–t*) differences occur, which appear to be related to the insulating nature of the oxide matrix itself and the respective band offsets. For both dopants a slight room-temperature PL quenching is observed, becoming strong only for dopant concentrations beyond 1 atom %. This circumstance together with the absence of the spectral behaviour expected for doped NCs indicates that dopant-induced defects are the origin of PL quenching, in accordance with theoretical DFT predictions. Low-temperature PL spectroscopy and transient transmission measurements show no indications for dopant-induced free carriers in Si NCs. Electrical measurements on MOS-capacitors

with additional injection blocking layers prove that E-fields in the range of 0.3–0.5 MV/cm are required to ionize the small fraction of lattice-incorporated dopants and to generate charge carriers. It was shown that the higher resistivity of the N-free oxide as compared to oxynitride masks the field-induce charge carrier generation from B-doped NCs. Comparing P-doped NCs in both matrices this effect was not found.

Summarizing the results reported here and previously [29,30,41,52] it turns out that P- and B-dopants in oxide-embedded Si NCs remain predominantly on interstitial lattice sites where they cannot be ionized by thermal energy at room-temperature, in agreement with the nanoscale-effects of self-purification, quantum- and dielectric confinement. This results in diminutive doping efficiencies [57]. We note that broader NC size distributions with tails towards the  $\approx 10$  nm range [58] or percolated nano-Si networks [53] are not subject to the same strong confinement conditions, so that measurable free carrier densities are likely.

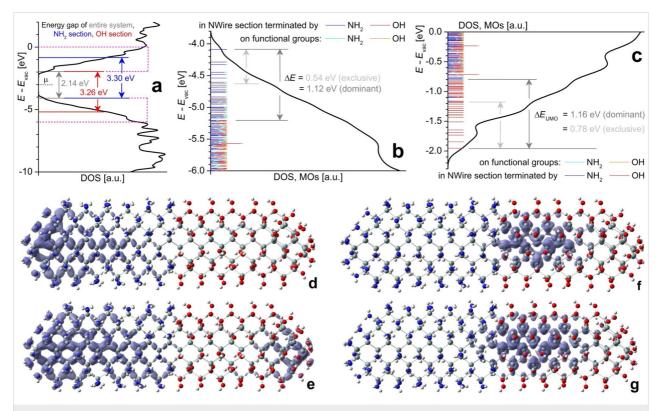

The fundamental inability of efficient conventional impurity doping at the bottom end of the nanoscale requires different doping approaches that either relocate the dopants in the surrounding matrix (e.g., Si modulation doping by  $SiO_2:Al$ ) [59] or do not require impurities at all (e.g., electrically reconfigurable nanowire-FETs [60] or p/n-behaviour induced by energy offsets created by locally  $Si_3N_4$  and  $SiO_2$  embedded Si-nanowires [61]).

#### **Supporting Information**

#### Supporting Information File 1

Additional figures.

[https://www.beilstein-journals.org/bjnano/content/supplementary/2190-4286-9-141-S1.pdf]

#### Acknowledgements

D.H. thanks the Alexander von Humboldt Foundation for a Feodor Lynen Fellowship. D.H. and M.K. acknowledge the German Research Foundation (DFG) for funding (HI 1779/3-1, KO 1220/22-1). D.H., J.L.-V. and D.K. acknowledge funding by the DAAD–Universities Australia joint research cooperation scheme 2016 (57215687). K.N. acknowledges the facilities and the scientific and technical assistance of the Australian Microscopy & Microanalysis Research Facility at the Australian Centre for Microscopy & Microanalysis at the University of Sydney.

#### ORCID® iDs

Daniel Hiller - https://orcid.org/0000-0001-8774-4069

Tomáš Chlouba - https://orcid.org/0000-0002-8383-1293

František Trojánek - https://orcid.org/0000-0003-2174-6402

Sebastian Gutsch - https://orcid.org/0000-0003-2468-7495

Dirk König - https://orcid.org/0000-0001-5485-9142

Petr Malý - https://orcid.org/0000-0001-9101-9548

#### References

- König, D. The Introduction of Majority Carriers into Group IV Nanocrystals. In *Nanotechnology and Photovoltaic Devices*; Valenta, J.; Mirabella, S., Eds.; Pan Stanford: Singapore, 2015; pp 203–254.

- Diarra, M.; Niquet, Y.-M.; Delerue, C.; Allan, G. Phys. Rev. B 2007, 75, 045301. doi:10.1103/PhysRevB.75.045301

- Cantele, G.; Degoli, E.; Luppi, E.; Magri, R.; Ninno, D.; Iadonisi, G.; Ossicini, S. *Phys. Rev. B* 2005, 72, 113303. doi:10.1103/PhysRevB.72.113303

- 4. König, D. AIP Adv. 2016, 6, 085306. doi:10.1063/1.4960994

- Perez-Wurfl, I.; Ma, L.; Lin, D.; Hao, X.; Green, M. A.; Conibeer, G. Sol. Energy Mater. Sol. Cells 2012, 100, 65–68. doi:10.1016/j.solmat.2011.02.029

- Wu, L.; Puthen-Veettil, B.; Nomoto, K.; Hao, X.; Jia, X.; Lin, Z.;

Yang, T. C.; Zhang, T.; Gutsch, S.; Conibeer, G.; Perez-Wurfl, I.

J. Appl. Phys. 2016, 119, 063102. doi:10.1063/1.4941695

- Mimura, A.; Fujii, M.; Hayashi, S.; Kovalev, D.; Koch, F. Phys. Rev. B 2000, 62, 12625. doi:10.1103/PhysRevB.62.12625

- Mangolini, L.; Thimsen, E.; Kortshagen, U. Nano Lett. 2005, 5, 655–659. doi:10.1021/nl050066y

- Hessel, C. M.; Henderson, E. J.; Veinot, J. G. C. Chem. Mater. 2006, 18, 6139–6146. doi:10.1021/cm0602803

- Perego, M.; Seguini, G.; Arduca, E.; Frascaroli, J.; De Salvador, D.; Mastromatteo, M.; Carnera, A.; Nicotra, G.; Scuderi, M.; Spinella, C.; Impellizzeri, G.; Lenardi, C.; Napolitani, E. *Nanoscale* 2015, 7, 14469–14475. doi:10.1039/C5NR02584B

- 11. Arduca, E.; Perego, M. *Mater. Sci. Semicond. Process.* **2017**, *62*, 156–170. doi:10.1016/j.mssp.2016.10.054

- Rowe, D. J.; Jeong, J. S.; Mkhoyan, K. A.; Kortshagen, U. R. Nano Lett. 2013, 13, 1317–1322. doi:10.1021/nl4001184

- Zhou, S.; Pi, X.; Ni, Z.; Ding, Y.; Jiang, Y.; Jin, C.; Delerue, C.;

Yang, D.; Nozaki, T. ACS Nano 2015, 9, 378–386.

doi:10.1021/nn505416r

- Kramer, N. J.; Schramke, K. S.; Kortshagen, U. R. Nano Lett. 2015, 15, 5597–5603. doi:10.1021/acs.nanolett.5b02287

- Ni, Z.; Pi, X.; Zhou, S.; Nozaki, T.; Grandidier, B.; Yang, D.

Adv. Opt. Mater. 2016, 4, 700–707. doi:10.1002/adom.201500706

- Hartel, A. M.; Hiller, D.; Gutsch, S.; Löper, P.; Estradé, S.; Peiró, F.; Garrido, B.; Zacharias, M. *Thin Solid Films* 2011, *520*, 121–125. doi:10.1016/j.tsf.2011.06.084

- Laube, J.; Gutsch, S.; Hiller, D.; Bruns, M.; Kübel, C.; Weiss, C.;

Zacharias, M. J. Appl. Phys. 2014, 116, 223501.

doi:10.1063/1.4904053

- Jivanescu, M.; Hiller, D.; Zacharias, M.; Stesmans, A. EPL 2011, 96, 27003. doi:10.1209/0295-5075/96/27003

- Gnaser, H. J. Vac. Sci. Technol., A 1994, 12, 452–456. doi:10.1116/1.579262

- Khelifi, R.; Mathiot, D.; Gupta, R.; Muller, D.; Roussel, M.; Duguay, S. Appl. Phys. Lett. 2013, 102, 013116. doi:10.1063/1.4774266

- Talbot, E.; Lardé, R.; Pareige, P.; Khomenkova, L.; Hijazi, K.; Gourbilleau, F. *Nanoscale Res. Lett.* **2013**, *8*, 39. doi:10.1186/1556-276X-8-39

- Hellman, O. C.; Vandenbroucke, J. A.; Rüsing, J.; Isheim, D.;

Seidman, D. N. Microsc. Microanal. 2000, 6, 437–444.

- Gnaser, H.; Gutsch, S.; Wahl, M.; Schiller, R.; Kopnarski, M.; Hiller, D.;

Zacharias, M. J. Appl. Phys. 2014, 115, 034304.

doi:10.1063/1.4862174

- 24. Nomoto, K.; Hiller, D.; Gutsch, S.; Ceguerra, A. V.; Breen, A.; Zacharias, M.; Conibeer, G.; Perez-Wurfl, I.; Ringer, S. P. Phys. Status Solidi RRL 2017, 11, 1600376. doi:10.1002/pssr.201600376

- Nomoto, K.; Gutsch, S.; Ceguerra, A. V.; Breen, A.; Sugimoto, H.;

Fujii, M.; Perez-Wurfl, I.; Ringer, S. P.; Conibeer, G. MRS Commun.

2016, 6, 283–288. doi:10.1557/mrc.2016.37

- Nomoto, K.; Sugimoto, H.; Breen, A.; Ceguerra, A. V.; Kanno, T.;

Ringer, S. P.; Perez Wurfl, I.; Conibeer, G.; Fujii, M. J. Phys. Chem. C

2016, 120, 17845–17852. doi:10.1021/acs.jpcc.6b06197

- Vurpillot, F.; Bostel, A.; Blavette, D. Appl. Phys. Lett. 2000, 76, 3127–3129. doi:10.1063/1.126545

- Talbot, E.; Lardé, R.; Gourbilleau, F.; Dufour, C.; Pareige, P. EPL

2009, 87, 26004. doi:10.1209/0295-5075/87/26004

- Hiller, D.; López-Vidrier, J.; Gutsch, S.; Zacharias, M.; Nomoto, K.;

König, D. Sci. Rep. 2017, 7, 863. doi:10.1038/s41598-017-01001-1

- Hiller, D.; López-Vidrier, J.; Gutsch, S.; Zacharias, M.; Wahl, M.;

Bock, W.; Brodyanski, A.; Kopnarski, M.; Nomoto, K.; Valenta, J.;

König, D. Sci. Rep. 2017, 7, 8337. doi:10.1038/s41598-017-08814-0

- Melkonyan, D.; Fleischmann, C.; Arnoldi, L.; Demeulemeester, J.; Kumar, A.; Bogdanowicz, J.; Vurpillot, F.; Vandervorst, W. *Ultramicroscopy* 2017, 179, 100–107. doi:10.1016/j.ultramic.2017.04.006

- Zanuttini, D.; Blum, I.; Rigutti, L.; Vurpillot, F.; Douady, J.; Jacquet, E.; Anglade, P.-M.; Gervais, B. J. Chem. Phys. 2017, 147, 164301. doi:10.1063/1.5001113

- Gault, B.; Saxey, D. W.; Ashton, M. W.; Sinnott, S. B.;

Chiaramonti, A. N.; Moody, M. P.; Schreiber, D. K. New J. Phys. 2016, 18, 033031. doi:10.1088/1367-2630/18/3/033031

- Carvalho, A.; Rayson, M. J.; Briddon, P. R. J. Phys. Chem. C 2012, 116, 8243–8250. doi:10.1021/jp300712v

- Guerra, R.; Ossicini, S. J. Am. Chem. Soc. 2014, 136, 4404–4409. doi:10.1021/ja5002357

- Valenta, J.; Greben, M.; Gutsch, S.; Hiller, D.; Zacharias, M. Appl. Phys. Lett. 2014, 105, 243107. doi:10.1063/1.4904472

- Valenta, J.; Greben, M.; Gutsch, S.; Hiller, D.; Zacharias, M.

J. Appl. Phys. 2017, 122, 144303. doi:10.1063/1.4999023

- Mangolini, L.; Jurbergs, D.; Rogojina, E.; Kortshagen, U. J. Lumin.

2006, 121, 327–334. doi:10.1016/j.jlumin.2006.08.068

- 39. Kachurin, G. A.; Cherkova, S. G.; Volodin, V. A.; Kesler, V. G.; Gutakovsky, A. K.; Cherkov, A. G.; Bublikov, A. V.; Tetelbaum, D. I. Nucl. Instrum. Methods Phys. Res., Sect. B 2004, 222, 497–504. doi:10.1016/j.nimb.2004.03.076

- Chen, X.; Pi, X.; Yang, D. J. Phys. Chem. C 2011, 115, 661–666. doi:10.1021/jp1102934

- König, D.; Gutsch, S.; Gnaser, H.; Wahl, M.; Kopnarski, M.;

Göttlicher, J.; Steininger, R.; Zacharias, M.; Hiller, D. Sci. Rep. 2015, 5,

9702. doi:10.1038/srep09702

- 42. Crowe, I. F.; Papachristodoulou, N.; Halsall, M. P.; Hylton, N. P.; Hulko, O.; Knights, A. P.; Yang, P.; Gwilliam, R. M.; Shah, M.; Kenyon, A. J. J. Appl. Phys. 2013, 113, 024304. doi:10.1063/1.4772947

- Hartel, A. M.; Gutsch, S.; Hiller, D.; Zacharias, M. Phys. Rev. B 2012, 85, 165306. doi:10.1103/PhysRevB.85.165306

- 44. Hartel, A. M.; Gutsch, S.; Hiller, D.; Zacharias, M. Phys. Rev. B 2013, 87, 035428. doi:10.1103/PhysRevB.87.035428

- Kozák, M.; Kořínek, M.; Trojánek, F.; Hiller, D.; Gutsch, S.;

Zacharias, M.; Malý, P. J. Appl. Phys. 2013, 114, 173103.

doi:10.1063/1.4829006

- Chlouba, T.; Trojánek, F.; Laube, J.; Hiller, D.; Gutsch, S.;

Zacharias, M.; Malý, P. Sci. Rep. 2018, 8, 1703.

doi:10.1038/s41598-018-19967-x

- Fukata, N.; Chen, J.; Sekiguchi, T.; Matsushita, S.; Oshima, T.;

Uchida, N.; Murakami, K.; Tsurui, T.; Ito, S. Appl. Phys. Lett. 2007, 90, 153117. doi:10.1063/1.2721377

- Pankove, J. I.; Wance, R. O.; Berkeyheiser, J. E. Appl. Phys. Lett. 1984, 45, 1100–1102. doi:10.1063/1.95030

- Johnson, N. M.; Herring, C.; Chadi, D. J. Phys. Rev. Lett. 1986, 56, 769–772. doi:10.1103/PhysRevLett.56.769

- Fukata, N.; Sasaki, S.; Fujimura, S.; Haneda, H.; Murakami, K. Jpn. J. Appl. Phys., Part 1 1996, 35, 3937–3941. doi:10.1143/JJAP.35.3937

- Holleman, A. F.; Wiberg, E.; Wiberg, N. Lehrbuch der Anorganischen Chemie, 101st ed.; Walter deGruyter: Berlin, Germany, 1995. doi:10.1515/9783110206845

- Gutsch, S.; Laube, J.; Hiller, D.; Bock, W.; Wahl, M.; Kopnarski, M.; Gnaser, H.; Puthen-Veettil, B.; Zacharias, M. Appl. Phys. Lett. 2015, 106, 113103. doi:10.1063/1.4915307

- Puthen-Veettil, B.; Zhang, T.; Chin, R. L.; Jia, X.; Nomoto, K.;

Yang, T. C.-J.; Lin, Z.; Wu, L.; Rexiati, R.; Gutsch, S.; Conibeer, G.;

Perez-Würfl, I. Appl. Phys. Lett. 2016, 109, 153106.

doi:10.1063/1.4964742

- Sychugov, I.; Valenta, J.; Mitsuishi, K.; Linnros, J. Phys. Rev. B 2012, 86, 075311. doi:10.1103/PhysRevB.86.075311

- Tanaka, T.; Kurosawa, Y.; Kadotani, N.; Takahashi, T.; Oda, S.; Uchida, K. *Nano Lett.* 2016, *16*, 1143–1149.

doi:10.1021/acs.nanolett.5b04406

- Seguini, G.; Schamm-Chardon, S.; Pellegrino, P.; Perego, M.

Appl. Phys. Lett. 2011, 99, 082107. doi:10.1063/1.3629813

- Stegner, A. R.; Pereira, R. N.; Lechner, R.; Klein, K.; Wiggers, H.;

Stutzmann, M.; Brandt, M. S. *Phys. Rev. B* **2009**, *80*, 165326.

doi:10.1103/PhysRevB.80.165326

- Almeida, A. J.; Sugimoto, H.; Fujii, M.; Brandt, M. S.; Stutzmann, M.; Pereira, R. N. *Phys. Rev. B* **2016**, 93, 115425.

doi:10.1103/PhysRevB 93.115425

- König, D.; Hiller, D.; Gutsch, S.; Zacharias, M.; Smith, S. Sci. Rep. 2017, 7, 46703. doi:10.1038/srep46703

- Heinzig, A.; Slesazeck, S.; Kreupl, F.; Mikolajick, T.; Weber, W. M. Nano Lett. 2012, 12, 119–124. doi:10.1021/nl203094h

- König, D.; Hiller, D.; Gutsch, S.; Zacharias, M. Adv. Mater. Interfaces

2014, 1, 1400359. doi:10.1002/admi.201400359

#### License and Terms

This is an Open Access article under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/4.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

The license is subject to the *Beilstein Journal of Nanotechnology* terms and conditions: (https://www.beilstein-journals.org/bjnano)

The definitive version of this article is the electronic one which can be found at:

doi:10.3762/bjnano.9.141

# The role of the Ge mole fraction in improving the performance of a nanoscale junctionless tunneling FET: concept and scaling capability

Hichem Ferhati<sup>1</sup>, Fayçal Djeffal<sup>\*1,2</sup> and Toufik Bentrcia<sup>2</sup>

#### Full Research Paper

Address:

<sup>1</sup>LEA, Department of Electronics, University Mostefa Benboulaid-Batna 2, Batna 05000, Algeria and <sup>2</sup>LEPCM, University of Batna 1, Batna 05000, Algeria

Email:

Fayçal Djeffal\* - faycal.djeffal@univ-batna2.dz

\* Corresponding author

Keywords:

ambipolar conduction; heterojunctions; junctionless tunneling field-effect transistor (JL TFET); nanoscale; SiGe

Beilstein J. Nanotechnol. **2018**, 9, 1856–1862. doi:10.3762/bjnano.9.177

Received: 06 February 2018 Accepted: 11 June 2018 Published: 22 June 2018

This article is part of the Thematic Series "Metrology and technology computer aided design for the sub-10 nm technology node".

Open Access

Guest Editor: P. Eyben

© 2018 Ferhati et al.; licensee Beilstein-Institut. License and terms: see end of document.

#### **Abstract**

In this paper, a new nanoscale double-gate junctionless tunneling field-effect transistor (DG-JL TFET) based on a  $Si_{1-x}Ge_x/Si/Ge$  heterojunction (HJ) structure is proposed to achieve an improved electrical performance. The effect of introducing the  $Si_{1-x}Ge_x$  material at the source side on improving the subthreshold behavior of the DG-JL TFET and on suppressing ambipolar conduction is investigated. Moreover, the impact of the Ge mole fraction in the proposed  $Si_{1-x}Ge_x$  source region on the electrical figures of merit (*FoMs*) of the transistor, including the swing factor and the  $I_{ON}/I_{OFF}$  ratio is analyzed. It is found that the optimized design with 60 atom % of Ge offers improved switching behavior and enhanced derived current capability at the nanoscale level, with a swing factor of 42 mV/dec and an  $I_{ON}/I_{OFF}$  ratio of 115 dB. Further, the scaling capability of the proposed  $Si_{1-x}Ge_x/Si/Ge$  DG-HJ-JL TFET structure is investigated and compared to that of a conventional Ge-DG-JL TFET design, where the optimized design exhibits an improved switching behavior at the nanoscale level. These results make the optimized device suitable for designing digital circuit for high-performance nanoelectronic applications.

#### Introduction

In the last years, the continuous miniaturization of nanoscale transistors induces new challenges including short-channel effects (SCEs) and high power consumption, which prevent incorporating conventional metal-oxide semiconductor field-effect transistors (MOSFETs) and their complements in nanoelectronic circuit designs [1-4]. In this context, small swing-

switch devices such as double-gate tunneling field-effect transistors (DG TFETs) are gaining attention because of their good subthreshold characteristics, high scalability and low OFF-current [5-8]. The main idea behind this innovative device is the use of a gated p-i-n diode, the working mechanism of which is based on a quantum band-to-band tunneling effect. This makes

it more immune against the undesired SCEs and enables a better scaling capability. Despite such attractive properties, DG TFETs still suffer from other issues mainly related to the relatively low ON-state current and the severe ambipolar conduction, which make it extremely challenging for designing highperformance digital nanocircuits [7-9]. Consequently, intensive efforts have been paid to address these limitations by proposing new designs based on heterostructures, gate engineering and high-k dielectrics [9-12]. Nanoscale DG TFETs are believed to face an upward amendment to meet the difficulty of decreasing the huge thermal budget required for the formation of the gated p-i-n diode structure. Moreover, in spite of the actual mature experimental techniques, realizing metallurgical junctions in sub-32 nm nodes is considered extremely difficult [13-15]. For this purpose, the junctionless (JL) design is considered the best approach to avoid the above outlined experimental limitations and achieve significant improvements regarding the transistor manufacturing cost [14-17]. The JL technology is considered to be cost-effective and allows avoiding the high thermal budget [15-17]. The concept of a gated source is used for the JL technology in order to ensure the band-to-band tunneling effect, while materials with high work function are required to generate the tunnel current. In other words, the channel is assumed to be a uniformly and highly doped n-type material, and in order to ensure the band-to-band tunneling effect, the source is supported with a control gate to make the device behave like a conventional p-i-n-based TFET [18]. However, the most pronounced drawbacks associated with the DG TFETs design also persist in the JL structure, namely the low ON-state current, the high leakage current and parasitic ambipolar conduction, which can eventually prevent the application in high-performance nanoelectronic circuits. The DG-JL TFET design can pave the way to reduce the fabrication cost, but it exhibits degraded electrical FoMs. Several recently published works are focused on improving the multi-gate JL TFET by suggesting design improvements such as gate underlap and overlap, introducing III-V materials and source/drain engineering [19-24]. Additional approaches are in fact required in order to push the limits of the DG-JL TFET performance and achieve energy-efficient and scalable transistors. To the best of our knowledge, no design approach based on Si<sub>1-x</sub>Ge<sub>x</sub>/Si/Ge heterochannels with optimized Ge content was proposed to improve the electrical performance and to suppress the parasitic ambipolar conduction in DG-JL TFETs. We present in this paper, a new DG-HJ-JL TFET design to achieve improved electrical FoMs and reduced fabrication cost. An exhaustive numerical study of the electrical behavior of the proposed device at the nanoscale level is performed using the ATLAS 2-D simulation software [25]. Further, the impact of the Ge content on the electrical performance of the transistor is investigated. It is found that the proposed design offers between improved

derived current capability and reduced ambipolar conduction compared to a conventional DG Ge-JL-TFET design. In order to consolidate our investigation, the scaling capability of the proposed design is investigated and compared to that of the conventional counterpart, where the proposed structure demonstrates a superior switching behavior. This makes the optimized structure a potential alternative for providing energy-efficient transistors with suppressed ambipolar conduction for designing high-performance nanoelectronic circuits at low manufacturing cost.

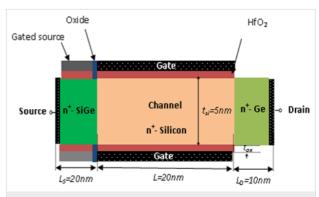

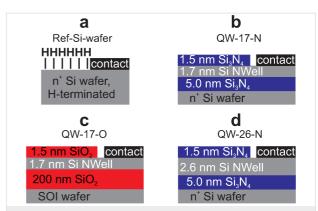

#### **Numerical Simulations**

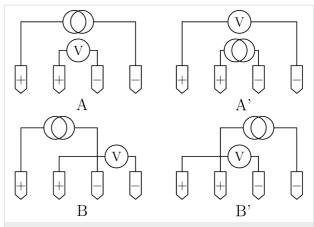

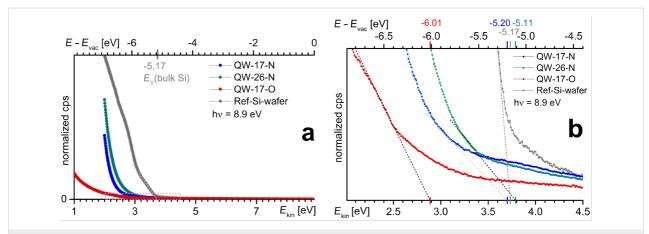

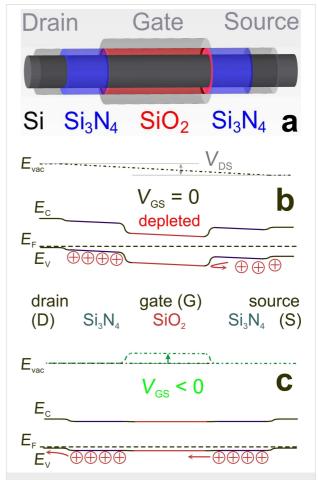

Figure 1 describes schematically the investigated DG-HJ-JL TFET structure. The cornerstone of the proposed design is the assumption of a uniformly and highly doped heterochannel (Si<sub>1-x</sub>Ge<sub>x</sub>/Si/Ge), which can be indicated by  $n^+/n^+/n^+$ . In addition, the proposed design is suggested with a HfO<sub>2</sub> gate dielectric in order to ensure a good electrostatic control of the channel, with  $t_{\rm ox}$  representing its thickness. Moreover, the material of the gated source is assumed to have a high work function value of 5.6 eV in order to guarantee the tunnel effect, while the work function of the channel gate is set equal to 4.3 eV. In Figure 1, L is the channel length,  $t_{\rm ch}$  refers to the channel thickness,  $N_{\rm d}$  is the doping concentration of the channel, and  $L_{\rm s}$  and  $L_{\rm d}$  denote the extension lengths of source and drain, respectively.

**Figure 1:** Schematic of the investigated DG-HJ-JL TFET with  $N_{\rm d}$  = 1·10<sup>19</sup> cm<sup>-3</sup> and  $t_{\rm ox}$  = 3 nm.

The accurate modeling of the nanoscale DG-HJ-JL TFET requires taking into account quantum-confinement effects, which lead to some modeling bottlenecks associated with the models of the carrier density gradient. Furthermore, since the investigated transistor is considered as a quantum mechanical device, complicated systems of equations resulted from the necessity of considering the band-to-band quantum tunneling effects. These nonlinear equations impose many mathematical difficulties, which complicate the analytical modeling of the nanoscale device performance. Numerical approaches are used

to deal with the above outlined problems. The ATLAS 2D device simulator using the S-PISCES module has emerged recently as a useful and realistic tool for numerically modeling the electrostatic behavior of transistors [25].

The electrostatic behavior of the investigated nanoscale  $(Si_{1-x}Ge_x/Si/Ge)$  DG-HJ-JL TFET including the tunnel effects is modeled using the nonlocal-BTBT command, which takes into account nonlocal band-to-band quantum tunneling [25]. In this perspective, the tunnel current is generated near the source/channel junction and can be characterized by a transfer of electrons and holes across this junction. Hence, the tunneling current for an electron with longitudinal energy E and transverse energy ET can be expressed as follows [25]:

$$J(E) = \frac{q}{\pi h} \iint T(E) \left[ (f_{\rm l} - f_{\rm r}) (E + E_{\rm T}) \right] \frac{\sqrt{m_{\rm e} m_{\rm h}}}{2\pi h^2} dE dE_{\rm T}, (1)$$

where T(E) represents the tunneling probability of the electrons, q is the electron charge,  $m_e$  and  $m_h$  are the effective masses of electrons and holes, respectively, h is the Planck constant.  $f_1$  and  $f_r$  are the Fermi–Dirac distributions on the left and the right side of the source/channel junction, respectively:

$$f_{1}(E) = \left[1 + \exp\left(\frac{E + E_{T} - E_{f\text{SiGe}}}{k_{B}T}\right)\right]^{-1},$$

$$f_{r}(E) = \left[1 + \exp\left(\frac{E + E_{T} - E_{f\text{Si}}}{k_{B}T}\right)\right]^{-1},$$

(2)

where,  $E_{f \text{SiGe}}$  and  $E_{f \text{Si}}$  are the Fermi levels at the  $\text{Si}_{1-x}\text{Ge}_x$  source and Si channel regions, respectively,  $k_{\text{B}}$  is the Boltzmann constant and T the temperature.

In order to reflect accurately the device behavior for very short dimensions like in our case, the modified drift—diffusion model, which includes other effects related to the short-channel nature of the investigated transistor and to quantum effects is used. Further, the gradient density model is also included, which consists of the quantum correction associated with the local potential to the carrier temperatures in the current equations [25]. Moreover, models for carrier recombination (Shockley–Read–Hall (SRH), Auger and surface recombination) are also adopted [26]. In fact, the carrier mobility mainly depends on three quantities, transverse and parallel electric field, doping and temperature, which were combined using Matthiessen's formula. Accordingly, the Lombardi model (CVT) is used to express the carrier mobility in the channel [27]. Moreover, the intrinsic parameters of the materials (Si,

$Si_{1-x}Ge_x$  and Ge) such as band gap, mobility and the density of states were considered to be dependent on the Ge mole fraction ( $x_{Ge}$ ). It should be noted that the Ge mole fraction is varied from 0 to 0.7. This corresponds to the experimental limit for growing  $Si_{1-x}Ge_x$  when avoiding interfacial defects at the considered device thickness  $t_{ch} = 5$  nm [28].

#### Results and Discussion

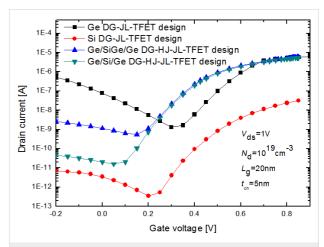

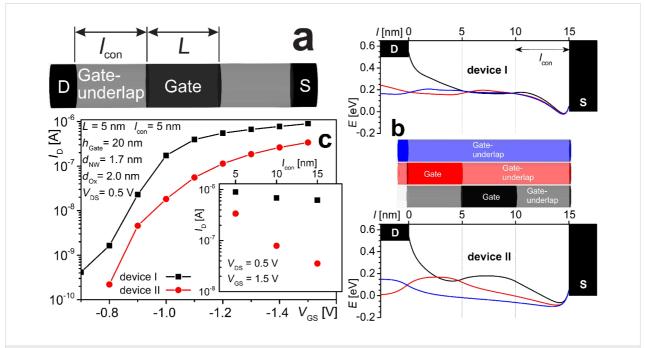

The main idea behind the proposed design is a modified heterostructured channel. In this context, it seems important to analyze the electrical behavior of the proposed design with considering different material configurations at the source, drain and channel regions in order to distinguish which heterochannel design provides the best electrical performance. Figure 2 depicts  $I_{\rm ds}-V_{\rm gs}$  characteristics of the proposed design with different material configurations of the heterochannel compared to that of the conventional designs with  $L_{\rm g}=20$  nm,  $L_{\rm s}=10$  nm and  $N_{\rm d}=1\cdot10^{19}$  cm<sup>-3</sup>.

**Figure 2:** Drain current as a function of the applied gate voltage for the DG-HJ-JL TFET proposed with different heterochannel configurations compared to that of the conventional homochannel designs ( $L_{\rm g} = 20 \, {\rm nm}, \, L_{\rm s} = 10 \, {\rm nm}$  and  $N_{\rm d} = 1 \cdot 10^{19} \, {\rm cm}^{-3}, \, t_{\rm ch} = 5 \, {\rm nm}$  and  $V_{\rm ds} = 1 \, {\rm V}$ ).

The proposed DG-HJ-JL TFET design with Ge/Si/Ge channel structure exhibits better electrostatic behavior and less parasitic ambipolar conduction than the other designs. In fact, this behavior can be attributed to two essential effects: Firstly, the enhanced tunneling current resulting from the low tunneling barrier giving rise to a higher probability of electron transfer at the source/channel interface. Secondly, the heterostructure at the channel/drain interface can be beneficial for sufficiently enlarging the tunneling barrier under reverse-bias conditions in order to effectively suppress the undesired ambipolar conduction. Moreover, we can notice that the conventional design with Si channel shows a reduced OFF-state current compared to that of the investigated heterochannel designs, which is mainly due

to the high band-gap energy and the low electron mobility associated to Si. On the other hand, the conventional Ge-DG-JL TFET design provides higher ON-state current. This is due to the smaller band gap energy of Ge, yielding a higher tunneling efficiency. Moreover, the higher electron mobility of Ge (3900 cm<sup>2</sup>·V<sup>-1</sup>·s<sup>-1</sup>) contributes to the increased drain current at the threshold voltage as compared to the conventional design with silicon (1400 cm<sup>2</sup>·V<sup>-1</sup>·s<sup>-1</sup>) channel. A suitable choice of the channel material can offer the possibility of enhancing the  $I_{\rm ON}/I_{\rm OFF}$  ratio as well as achieving a lower swing factor. For this purpose, introducing Si<sub>1-x</sub>Ge<sub>x</sub> material at the source side can be useful for achieving an improved electrical behavior through modulating the tunneling barrier width at the source/channel junction by varying the Ge concentration.

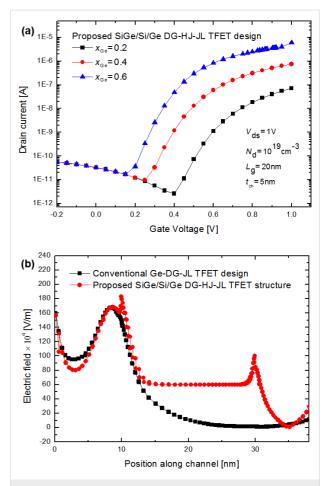

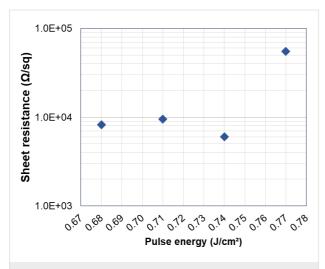

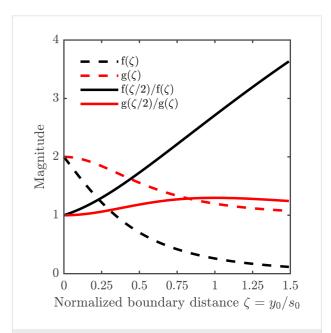

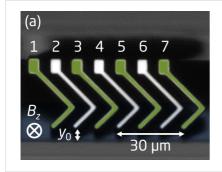

Figure 3a shows the transfer characteristics associated of the proposed Si<sub>1-x</sub>Ge<sub>x</sub>/Si/Ge DG-HJ-JL TFET design with different Ge mole fractions. Increasing the Ge content leads to an increase of the drain current. This is mainly due to the enhanced carrier mobility caused by the increased Ge content. Moreover, introducing SiGe at the source side can be effective for reducing the tunneling barrier. Besides, the Ge concentration increase induces a lowering of the tunneling barrier, which enables enhancing the derived current capability as shown in Figure 3a. It can be also concluded that the Ge mole fraction modulates the threshold voltage for the tunnel-current generation, which can in turn influence greatly the subthreshold behavior of the device. Moreover, the proposed Si<sub>1-x</sub>Ge<sub>x</sub>/Si/Ge heterochannel enables a superior control of the channel conductivity through modulating the electric field at the heterojunction interfaces. In this regard, it is of great importance to illustrate the electric field distribution for a better understanding of the physical rules governing the obtained improvements of the electrostatic behavior. Figure 3b compares the distribution of the electric field along the channel of the proposed Si<sub>1-x</sub>Ge<sub>x</sub>/Si/Ge DG-HJ-JL TFET design to that of the conventional Ge-DG-JL TFET counterpart. Clearly, a considerable change in the electric field distribution can be achieved by including the heterochannel, with higher electric field arising in the source/ channel interface as well as along the channel. This indicates that by a proper choice of the channel material, we can achieve an enhanced electrostatic behavior. This enables improving the carrier transport efficiency and thereby the device derived current capability at the nanoscale level.

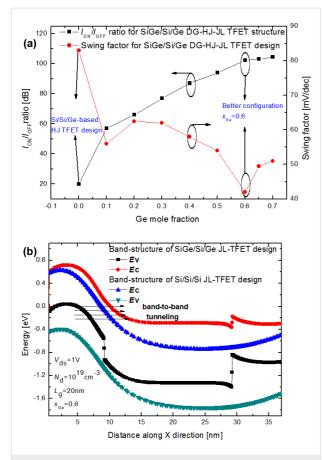

In order to get a qualitative idea about the impact of the Ge concentration on the electrical performance of the proposed DG-HJ-JL TFET design, Figure 4a shows both  $I_{\rm ON}/I_{\rm OFF}$  ratio and the subthreshold swing factor as functions of the Ge mole fraction. By increasing the Ge content, the  $I_{\rm ON}/I_{\rm OFF}$  ratio increases significantly to reach its maximum for a Ge mole frac-

**Figure 3:** (a) Transfer characteristics of the proposed  $Si_{1-x}Ge_x/Si/Ge$  DG-HJ-JL TFET as a function of the Ge concentration with  $N_{\rm d}=1\cdot 10^{19}~{\rm cm}^{-3},~V_{\rm ds}=1~{\rm V},~t_{\rm ox}=2~{\rm nm},~L_{\rm g}=20~{\rm nm}$  and  $t_{\rm ch}=5~{\rm nm}.$  (b) Distribution of the electric field along the channel of the proposed  $Si_{1-x}Ge_x/Si/Ge$  DG-HJ-JL TFET structure and the conventional Ge-DG-JL TFET design with  $N_{\rm d}=1\cdot 10^{19}~{\rm cm}^{-3},~t_{\rm ch}=5~{\rm nm},~t_{\rm ox}=2~{\rm nm},~L_{\rm g}=20~{\rm nm}$  and  $L_{\rm s}=10~{\rm nm}.$

tion value of 0.6 and saturates after this value. Moreover, the  $I_{\rm ON}/I_{\rm OFF}$  ratio of the proposed DG-HJ-JL TFET is higher than that of the conventional structure with uniform channel. This can be attributed to the enhanced tunneling current resulting from the change of the tunneling barrier with increasing Ge content. Figure 4b compares the band diagrams of the DG-HJ-JL TFET design and the conventional structure with uniform Si channel. Figure 4b reveals that by introducing  $\mathrm{Si}_{1-x}\mathrm{Ge}_x$ , the tunneling barrier height at the source–channel junction decreases and a higher tunneling current can be generated when the band alignment at the junction is satisfied.

In addition, Figure 4 shows the complex subthreshold behavior. The Ge mole fraction induces a highly non-linear behavior of the swing factor as it is shown in Figure 4a. This phenomenon can be ascribed to the quantum nature of the band-to-band tunneling effects, and determining the Ge concentration that

**Figure 4:** (a) Subthreshold swing factor and the  $I_{ON}/I_{OFF}$  ratio as functions of the Ge mole fraction for the investigated  $\mathrm{Si}_{1-x}\mathrm{Ge}_x/\mathrm{Si}/\mathrm{Ge}$  DG-HJ-JL TFET structure with  $N_{\rm d}=1\cdot10^{19}$  cm<sup>-3</sup>,  $V_{\rm ds}=1$  V,  $t_{\rm ox}=2$  nm,  $L_{\rm g}=20$  nm and  $t_{\rm ch}=5$  nm. (b) Comparison of the band diagrams of the proposed  $\mathrm{Si}_{1-x}\mathrm{Ge}_x/\mathrm{Si}/\mathrm{Ge}$  DG-HJ-JL TFET design and the conventional structure with uniform Si channel.

provides an enhanced subthreshold behavior seems to be very complex at the nanoscale level. The swing factor decreases significantly above  $x_{\rm Ge}=0.3$ , which can be explained by the effect of the tunneling barrier height on the device subthreshold behavior. At a Ge mole fraction of 0.6, a good trade-off between derived current capability and subthreshold behavior is obtained, with an  $I_{\rm ON}/I_{\rm OFF}$  ratio value of 115 dB and a swing factor value of 42 mV/dec at the nanoscale level ( $L_{\rm g}=20$ nm) as it is illustrated in Figure 4a.

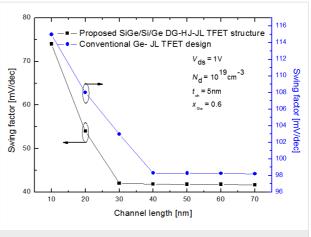

More importantly, we analyze the impact of the optimized  $Si_{1-x}Ge_x/Si/Ge$  heterochannel structure on the device scaling capability for high-performance nanoelectronic applications. Figure 5 depicts the swing factor as a function of the transistor channel length for both the proposed  $Si_{1-x}Ge_x/Si/Ge$  DG-HJ-JL TFET design and the conventional Ge-DG-JL TFET structure with  $t_{\rm ch} = 5$  nm,  $x_{\rm Ge} = 0.6$  and  $N_{\rm d} = 1\cdot10^{19}$  cm<sup>-3</sup>. The optimized design provides better scaling capability than the conventional one and exhibits a faster decrease of the swing factor as a

**Figure 5:** Subthreshold swing factor as a function of the channel length for both the proposed  $\mathrm{Si}_{1-x}\mathrm{Ge}_x/\mathrm{Si}/\mathrm{Ge}$  DG-HJ-JL TFET and the conventional Ge-DG-JL TFET with  $N_\mathrm{d}$  = 1·10<sup>19</sup> cm<sup>-3</sup>,  $V_\mathrm{ds}$  = 1 V,  $t_\mathrm{ox}$  = 2 nm,  $L_\mathrm{S}$  = 10 nm and  $t_\mathrm{ch}$  = 5nm.

function of the channel length. This behavior can be explained by the improved electrostatic response offered by the heterochannel.

For the completeness of this work, we analyze the improvements of the proposed design compared to conventional TFET devices with regard to the electrical performance. Table 1 summarizes an overall comparison of electrical metrics between the proposed  $Si_{1-x}Ge_x/Si/Ge$  DG-HJ-JL TFET, the conventional Ge-DG-JL TFET design and the numerical results associated to the conventional Si-DG-JL TFET [18]. it reveals that the proposed design with heterochannel outperforms considerably the conventional counterparts, with 58% improvement regarding the subthreshold swing factor and 54% enhancement in terms of the  $I_{\rm ON}/I_{\rm OFF}$  ratio. The optimized design improves the device tunneling performance, not only through a more effective carrier-transport mechanism, but also through a distinctive reduction of the undesired ambipolar conduction.

#### Conclusion

In this work, a new DG-JL TFET design with a heterochannel (Si<sub>1-x</sub>Ge<sub>x</sub>/Si/Ge) has been proposed as a new way to achieve enhanced electrical performance and suppressed ambipolar conduction. It has been concluded from the obtained results that the investigated DG-HJ-JL TFET design offers the possibility to overcome the trade-off between improved switching characteristic and superior derived current capability. In addition, the impact of the Ge concentration on the electrical behavior of the device has been analyzed. It has been deduced that the proposed design with 60% of Ge provides an  $I_{\rm ON}/I_{\rm OFF}$  ratio of 115 dB and a swing factor of 42 mV/dec. It has been also concluded that the optimized design offers superior scaling capability compared to the conventional Ge-DG-JL TFET structure.

|                                                                 | conventional Ge-DG-JL<br>TFET design | proposed Si <sub>1-x</sub> Ge <sub>x</sub> /Si/Ge<br>DG-HJ-JL TFET structure | conventional Si-JL<br>TFET structure [18 |

|-----------------------------------------------------------------|--------------------------------------|------------------------------------------------------------------------------|------------------------------------------|

| design variables                                                |                                      |                                                                              |                                          |

| channel length $L_{g}$ (nm)                                     | 20                                   | 20                                                                           | 20                                       |

| source/drain extensions length L <sub>s/d</sub> (nm)            | 10                                   | 10                                                                           | 25                                       |

| dielectric permittivity                                         | 25                                   | 25                                                                           | 25                                       |

| oxide thickness $t_{ox}$ (nm)                                   | 2                                    | 2                                                                            | 2                                        |

| channel thickness t <sub>ch</sub> (nm)                          | 5                                    | 5                                                                            | 5                                        |

| gate work function (eV)                                         | 4.3                                  | 4.3                                                                          | 4.3                                      |

| gated source work function (eV)                                 | 5.6                                  | 5.6                                                                          | 5.9                                      |

| channel doping concentration N <sub>d</sub> (cm <sup>-3</sup> ) | 1·10 <sup>19</sup> , n-type          | 1·10 <sup>19</sup> , n-type                                                  | 1·10 <sup>19</sup> , n-type              |

| drain voltage V <sub>ds</sub> (V)                               | 1                                    | 1                                                                            | 1                                        |

| Ge mole fraction of Si <sub>1-x</sub> Ge <sub>x</sub> source    | _                                    | 60                                                                           | _                                        |

| performance parameters                                          |                                      |                                                                              |                                          |

| subthreshold swing (mV/dec)                                     | 114                                  | 42                                                                           | 81                                       |

| I <sub>ON</sub> /I <sub>OFF</sub> ratio (dB)                    | 79                                   | 115                                                                          | 98                                       |

| ambipolar conduction                                            | high                                 | suppressed                                                                   | high                                     |

Therefore, the optimized design opens up the route for achieving an enhanced derived current capability with suppressed ambipolar conduction and for improving the device subthreshold behavior at the nanoscale level. This makes the optimized  $\mathrm{Si}_{1-x}\mathrm{Ge}_x/\mathrm{Si}/\mathrm{Ge}$  DG-HJ-JL TFET design a potential alternative for high-performance nanoelectronic applications. Moreover, this study can be extended by investigating the impact of other parameters such as the interfacial defects between both Si and SiGe materials and the degradation-related ageing effects including stress. To do so, new complex models and numerical simulations need to be developed.

#### References

- International Technology Roadmap for Semiconductors ITRS 2.0 Home Page. http://itrs2.net (accessed June 8, 2018).

- Chen, Q.; Meindl, J. D. Nanotechnology 2004, 15, S549. doi:10.1088/0957-4484/15/10/009

- Frank, D. J.; Dennard, R. H.; Nowak, E.; Solomon, P. M.; Taur, Y.;

Wong, H.-S. P. Proc. IEEE 2001, 89, 259–288. doi:10.1109/5.915374

- Mamaluy, D.; Gao, X. Appl. Phys. Lett. 2015, 106, 193503. doi:10.1063/1.4919871

- Ionescu, A. M.; Riel, H. Nature 2011, 479, 329–337. doi:10.1038/nature10679

- Seabaugh, A. C.; Zhang, Q. Proc. IEEE 2010, 98, 2095–2110. doi:10.1109/JPROC.2010.2070470

- Choi, W. Y.; Park, B.-G.; Lee, J. D.; Liu, T.-J. K. IEEE Electron Device Lett. 2007, 28, 743–745. doi:10.1109/LED.2007.901273

- Avci, U. E.; Morris, D. H.; Young, I. A. IEEE J. Electron Devices Soc. 2015, 3, 88–95. doi:10.1109/JEDS.2015.2390591

- Esseni, D.; Guglielmini, M.; Kapidani, B.; Rollo, T.; Alioto, M. *IEEE Trans. VLSI Syst.* 2014, 22, 2488–2498. doi:10.1109/TVLSI.2013.2293135

- Seema; Chauhan, S. S. Superlattices Microstruct. 2018, 117, 1–8. doi:10.1016/j.spmi.2018.03.002

- 11. Abdi, D. B.; Kumar, M. J. *IEEE J. Electron Devices Soc.* **2014**, *2*, 187–190. doi:10.1109/JEDS.2014.2327626

- Gundapaneni, S.; Bajaj, M.; Pandey, R. K.; Murali, K. V. R. M.; Ganguly, S.; Kottantharayil, A. *IEEE Trans. Electron Devices* 2012, 59, 1023–1029. doi:10.1109/TED.2012.2185800

- 13. Boucart, K.; Ionescu, A. M. *IEEE Trans. Electron Devices* **2007**, *54*, 1725–1733. doi:10.1109/TED.2007.899389

- Chebaki, E.; Djeffal, F.; Ferhati, H.; Bentrcia, T. Superlattices Microstruct. 2016, 92, 80–91. doi:10.1016/j.spmi.2016.02.009

- Djeffal, F.; Ferhati, H.; Bentrcia, T. Superlattices Microstruct. 2016, 90, 132–140. doi:10.1016/j.spmi.2015.09.041

- Lee, C.-W.; Afzalian, A.; Akhavan, N. D.; Yan, R.; Ferain, I.;

Colinge, J.-P. Appl. Phys. Lett. 2009, 94, 053511.