# A look underneath the SiO<sub>2</sub>/4H-SiC interface after N<sub>2</sub>O thermal treatments

Patrick Fiorenza<sup>\*1</sup>, Filippo Giannazzo<sup>1</sup>, Lukas K. Swanson<sup>1</sup>, Alessia Frazzetto<sup>2,3</sup>, Simona Lorenti<sup>3</sup>, Mario S. Alessandrino<sup>3</sup> and Fabrizio Roccaforte<sup>1</sup>

| Full Research Paper                                                                                                                                       | Open Access                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Address:                                                                                                                                                  | Beilstein J. Nanotechnol. 2013, 4, 249–254.                                 |

| <sup>1</sup> Consiglio Nazionale delle Ricerche - Istituto per la Microelettronica e<br>Microsistemi (CNR-IMM) Strada VIII n. 5, Zona Industriale, 95121, | doi:10.3762/bjnano.4.26                                                     |

| Catania, Italy, <sup>2</sup> Scuola Superiore di Catania - Università degli Studi di                                                                      | Received: 16 November 2012                                                  |

| Catania, Via Valdisavoia 9, 95123, Catania, Italy and                                                                                                     | Accepted: 26 March 2013                                                     |

| <sup>3</sup> STMicroelectronics, Stadale Primosole 50, 95121, Catania, Italy                                                                              | Published: 08 April 2013                                                    |

| Email:                                                                                                                                                    | This article is part of the Thematic Series "High-resolution electrical and |

| Patrick Fiorenza <sup>*</sup> - patrick.fiorenza@imm.cnr.it                                                                                               | chemical characterization of nm-scale organic and inorganic devices".       |

| * Corresponding author                                                                                                                                    | Guest Editors: E. Meyer and P. Eyben                                        |

| Keywords:                                                                                                                                                 | © 2013 Fiorenza et al; licensee Beilstein-Institut.                         |

| 4H-SiC; metal/oxide/semiconductor; nitrogen incorporation                                                                                                 | License and terms: see end of document.                                     |

# Abstract

The electrical compensation effect of the nitrogen incorporation at the  $SiO_2/4H$ -SiC (p-type) interface after thermal treatments in ambient N<sub>2</sub>O is investigated employing both scanning spreading resistance microscopy (SSRM) and scanning capacitance microscopy (SCM). SSRM measurements on p-type 4H-SiC areas selectively exposed to N<sub>2</sub>O at 1150 °C showed an increased resistance compared to the unexposed ones; this indicates the incorporation of electrically active nitrogen-related donors, which compensate the p-type doping in the SiC surface region. Cross-sectional SCM measurements on SiO<sub>2</sub>/4H-SiC metal/oxide/semiconductor (MOS) devices highlighted different active carrier concentration profiles in the first 10 nm underneath the insulator–substrate interface depending on the SiO<sub>2</sub>/4H-SiC roughness.

The electrically active incorporated nitrogen produces both a compensation of the acceptors in the substrate and a reduction of the interface state density ( $D_{it}$ ). This result can be correlated with the 4H-SiC surface configuration. In particular, lower  $D_{it}$  values were obtained for a SiO<sub>2</sub>/SiC interface on faceted SiC than on planar SiC. These effects were explained in terms of the different surface configuration in faceted SiC that enables the simultaneous exposition at the interface of atomic planes with different orientations.

# Introduction

The  $SiO_2/4H$ -SiC interface is the main building block of SiCbased MOSFET devices and its electrostructural quality typically has a direct impact on the device performance in powerelectronics applications. In particular, electrically active defects at the  $SiO_2/SiC$  interfaces, such as carbon clusters, silicon suboxide bonds, or intrinsic defects in the near-interfacial oxide

layers have been indicated as the origin of the commonly observed low-channel mobility in SiC MOSFETs [1,2]. To alleviate the mobility problem, different postoxidation annealings (POA) of the gate oxide in NO or N<sub>2</sub>O have been explored [3], which can be efficient to provide adequate mobility values in the range of 30–50 cm<sup>2</sup>·V<sup>-1</sup>·s<sup>-1</sup> [4,5], but still significantly lower than the theoretical limits.

While it is commonly accepted that POA treatments in ambient NO or N2O have a beneficial effect on the SiO2 insulator and on the SiO<sub>2</sub>/4H-SiC interface due to the passivation of oxide defects and interface traps by the incorporated nitrogen, the impact of these thermal treatments on the electrical properties of the 4H-SiC substrate is still under debate. Recently, Kosugi et al. [6] performed X-ray photoelectron spectroscopy (XPS) measurements on 4H-SiC directly exposed to ambient NO at 1200 °C, demonstrating that a significant density of nitrogen atoms (10<sup>14</sup> cm<sup>-3</sup>) is incorporated in the 4H-SiC near surface region and remains even after removing the thin (ca. 5 Å) SiO<sub>2</sub> layer formed on SiC during the annealing by sustained etching in hydrofluoric acid. The same group [7] demonstrated by the electrically detected magnetic resonance technique that shallow donor levels can be associated with a fraction of the incorporated N atoms. However, information on the electrical activation of the incorporated nitrogen and on the depth extension of the nitrogen profile is still lacking. Moreover, the role of the 4H-SiC surface morphology and in particular of the crystallographic planes exposed at the SiO<sub>2</sub>/4H-SiC interface on the nitrogen incorporation have to be clarified.

In this paper, we applied scanning spreading resistance microscopy (SSRM) and scanning capacitance microscopy (SCM) to get a deeper insight into the electrical activation of nitrogen incorporated into 4H-SiC during thermal treatments in N2O at 1150 °C. These two scanning probe methods have been applied in the past to study the electrical activation of ion doped and annealed SiC [8-11]. Due to the different measuring principles, i.e., differential capacitance measurements for SCM and current measurements for SSRM, the two techniques exhibit complementary performances especially in terms of dynamic range, with SSRM more suitable for higher concentrations and SCM more sensitive to lower concentrations, respectively. These complementary characters have been fully exploited in the present study. SSRM measurements were performed on p<sup>+</sup>-doped (≈10<sup>19</sup> cm<sup>-3</sup>) 4H-SiC areas selectively exposed to ambient N2O (without the presence of the gate oxide to maximize the effect of nitrogen incorporation), revealing a significant increase of the SiC resistivity with respect to unexposed areas, i.e., a compensation effect from the N-related donors. SCM measurements were performed also on p-doped  $(\approx 10^{17} \text{ cm}^{-3})$  4H-SiC exposed to ambient N<sub>2</sub>O through a 30 nm

thick gate oxide, to simulate the real metal/oxide/semiconductor stack used in the MOSFET device. To evaluate the impact of 4H-SiC surface morphology on the nitrogen incorporation, SiC samples with properly prepared *flat* or *faceted* surfaces were considered. Cross-sectional SCM measurements provided information on the depth extension of N-compensated 4H-SiC and revealed a more efficient compensation in the faceted 4H-SiC sample.

#### Description of the experiment

SSRM is employed to investigate the changes in the resistivity of p<sup>+</sup>-type doped 4H-SiC substrate regions selectively exposed to N<sub>2</sub>O at 1150 °C for four hours, with respect to unexposed ones. The results of this analysis demonstrate that during the low-temperature (1150 °C) thermal treatment, N atoms are incorporated in SiC and a fraction of them occupy a substitutional position, becoming electrically active and acting as donors. The role played by 4H-SiC surface morphology on N incorporation has also been investigated, considering two different samples with a smooth (flat) and with a macroscopically stepped (faceted) surface, respectively. Details of the surface preparation of the samples can be found in the experimental section. Cross-sectional scanning capacitance microscopy (SCM) was used to profile the active doping concentration in the SiC interfacial region of MOS devices, showing a higher compensation for the *faceted* sample than for the *flat* one. Recently, we demonstrated that MOS on the faceted surface exhibit also a lower interface-state density  $(\approx 3 \times 10^{11} \text{ cm}^{-2} \cdot \text{eV}^{-1})$  with respect to devices on the *flat* surface ( $\approx 7 \times 10^{11} \text{ cm}^{-2} \cdot \text{eV}^{-1}$ ) [12,13]. Here, both the different values of Dit at SiO<sub>2</sub>/4H-SiC interface and the different doping in the near interface SiC region have been explained in terms of the peculiar surface morphology of *faceted* samples, assuming a preferential nitrogen incorporation in the 4H-SiC substrate when it exposes a larger percentile of (11-2n) planes.

#### Results and Discussion

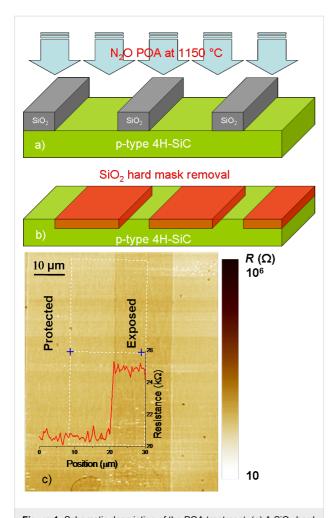

To gain an insight into the effect of nitrogen on SiC during the annealing in N<sub>2</sub>O, a patterned hard mask was defined onto a p<sup>+</sup>-type SiC surface (as described in the Experimental section) in order to obtain regions selectively exposed and unexposed to N<sub>2</sub>O. After the thermal treatment of the patterned samples (Figure 1a), the hard mask was removed (Figure 1b) followed by SSRM measurements on the bare SiC surface (Figure 1c) [14]. The SSRM map in Figure 1c shows a locally increased resistance in the SiC surface regions that were exposed to N<sub>2</sub>O relative to the regions that were protected by the hard mask. Hence, through SSRM we are able to directly demonstrate that the introduction of nitrogen at the surface of SiC by exposure to N<sub>2</sub>O and the low thermal budget (1150 °C) enables, surprisingly, a compensation effect that reduces the effective concen-

**Figure 1:** Schematic description of the POA treatment. (a) A SiO<sub>2</sub> hard mask is used to protect selectively the 4H-SiC during the POA. (b) After removal of the hard mask (by HF wet etch) on the 4H-SiC surface there are regions protected and exposed to the POA. (c) SSRM imaged on the patterned SiC surface; the two dimensional map of the substrate surface. The resistance line profile going from protected to exposed strips demonstrates a higher resistance value in the exposed region.

tration of p-type acceptors. Such a scenario has been previously proposed on the basis of physical measurements quantifying nitrogen incorporation and the reduction of  $D_{it}$  [3]. However, a direct measurement of the local electrical modifications has yet to be reported.

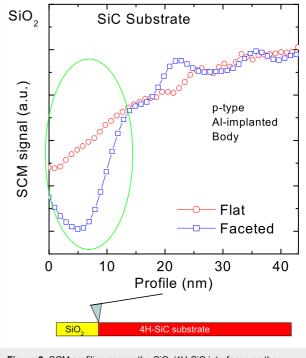

In the following it will be shown that this compensation effect due to nitrogen incorporation in the SiC near-surface region strongly depends on the SiC morphology, i.e., on the exposed planes at the interface with SiO<sub>2</sub>. High-resolution scanning capacitance microscopy across the interface region was applied to get a deeper insight into this aspect. Figure 2 shows the SCM signal versus depth profiles collected both on the *faceted* and *flat* samples in the 40 nm 4H-SiC region under the SiO<sub>2</sub>/SiC interface. The two depth profiles are laterally averaged over

Figure 2: SCM profiling across the SiO<sub>2</sub>/4H-SiC interfaces on the *faceted* (blue squares) and *flat* (red circles) samples respectively.

1  $\mu$ m. They are almost coincident for depths greater than about 20 nm, while they are significantly different in the SiC interfacial region up to about 15 nm, where the SCM signal in the *faceted* sample is lower than in the *flat* sample. The lower SCM signal indicates a higher compensation of Al acceptors, which is consistent with a more efficient incorporation of substitutional (electrically active) nitrogen atoms in SiC.

The simultaneous presence of different planes at the SiO<sub>2</sub>/4H-SiC interface in the *faceted* sample can be invoked to explain the better nitrogen incorporation during POA, leading to a more efficient passivation of interface traps and to a higher compensation of interfacial SiC. In fact, for a macroscopically stepped surface, the SiO<sub>2</sub>/SiC interface is not only formed on the basal plane (0001), but a significant fraction of the interface area is formed on the (11–2*n*) facets [15]. Accordingly, a different efficiency of nitrogen incorporation on the (0001) and (11–2*n*) facets during the POA process could explain the different  $D_{it}$  values in the two samples.

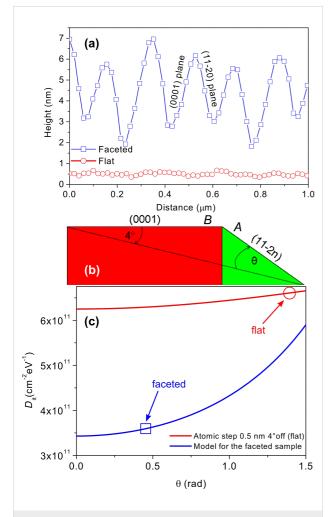

Figure 3a shows the morphology profiles (acquired by AFM data in [12]) of the 4H-SiC substrates surfaces both for the faceted (blue squares) and flat (red circles) samples respectively. The surface roughness (RMS) was 0.36 nm and 1.75 nm for the flat sample and for the faceted sample, respectively. The facets have a typical height of about 5 nm and their orientation is correlated to the original miscut direction of the wafers. In the present case, the substrates are cut along the (0001) basal plane with a 4° off-axis orientation toward the <11-20> direction. Each of these steps exposes both the (0001) basal plane and the plane along the <11-2n> direction. On the other hand, the flat sample shows no facets. The line profile in Figure 3a (circles) shows the typical 4H-SiC steps with ca. 0.5 nm height, corresponding to two Si–C pairs. This peculiar morphology of the interface can explain the macroscopic electrical behaviour of the capacitors ( $D_{it}$ ).

**Figure 3:** (a) AFM single scan line taken on the surfaces of the *faceted* and *flat* samples. (b) Schematic cross section of the basal-plane–facet orientation considering a 4° off-axis cut angle. (c) Simulated density of interface states for the ideal case and single atomic steps (red), and including the experimental measured facets (AFM section) changing the  $\theta$  (11–2*n*) facet orientation (blue). The calculated values are compared with the experimental values.

In fact, for our MOS capacitors fabricated on a faceted surface as in Figure 3a, a significant fraction of the total  $SiO_2/4H$ -SiC interface area is formed on (11-2n) planes, with lower  $D_{it}$  than the basal plane (0001). This latter can justify the reduced  $D_{it}$  in the faceted sample. Recently, Saitoh et al. demonstrated [15] the variation in the density of the interface states in MOS capacitors fabricated on 4H-SiC epilayers with different misorientation angles, moving from  $8^\circ$ , i.e., the (0001) largest basal plane, up to 90° toward the <11–20> direction, i.e., the (11–20) plane.

The  $D_{it}$  at 0.2 eV below the conduction band was found to decrease from  $D_{it,(0001);8^{\circ}-off axis} = 5 \times 10^{12} \text{ cm}^{-2} \cdot \text{eV}^{-1}$  for MOS capacitors fabricated on the (0001) face to  $D_{it,(11-20)} =$  $3 \times 10^{11} \text{ cm}^{-2} \cdot \text{eV}^{-1}$  for capacitors on the (11–20) face. By geometrical calculations based on the AFM morphology in Figure 3a, it was possible to estimate the weighted average between the impact of the (11–2*n*) and the (0001) interface areas in terms of the macroscopic  $D_{it}$  measured values. The real experimental 4H-SiC structure can be schematically described as in Figure 3b (cross-section configuration).

Considering an ideal  $D_{it,(0001)} = 1 \times 10^{12} \text{ cm}^{-2} \cdot \text{eV}^{-1}$  (for the 0° off-axis angle) at 0.2 eV from the conduction band edge, higher than the interface state density in the face (11–20), the total macroscopic density of interface states can be written:

$$D_{\text{it;macroscopic}} = n \left( D_{\text{it},(11-20)} \frac{A}{A+B} + D_{\text{it},(0001)} \frac{B}{A+B} \right) (1)$$

where

$$n = S / \left( B \cos \theta + A \cos \left( 90^{\circ} - \theta \right) \right)$$

(2)

And where S is a scale factor, A and B are the mean experimental dimensions of the (11-2n) facets and of the basal planes, respectively (taken from the AFM profiles in Figure 3a). Moreover, the angle  $\theta$  is the incremental angle with respect to the off-axis cut angle [16].

Equations 1 and 2 predict the total macroscopic  $D_{it}$ , which is the geometrically weighted average between the two limiting conditions, i.e., the interface state density along the (11–20) plane ( $D_{it,(11-20)}$ ) and the interface state density along the (0001) plane ( $D_{it,(0001)}$ ). For the flat sample the used parameters are based on A = 0.5 nm,  $B = A/\tan 4^\circ$  (4° miscut angle). The final  $D_{it}$  value is found taking the value for  $\theta = (90 - 4)^\circ$  because in the ideal case no facet is formed (Figure 3c). For the faceted sample the used parameters are based on A = 4.5 nm and B = 5.5 nm. The final  $D_{it}$  value can be found by taking the variable value  $\theta$  from 10–20°, because the facet is formed and its angle can vary between 10 and 20°, as reported in the literature [17]. The simulations explain perfectly the experimental results. Figure 3c compares the calculated curves that took to

account the geometrical configuration of the SiO<sub>2</sub>/4H-SiC interface in the two cases and the experimental  $D_{it}$  value measured on MOS prototypes. Recently, J. Rozen et al. [3] pointed out that the  $D_{it}$  reduction is strongly correlated to the nitrogen incorporation during the POA. Now it is possible to associate the lowering of the density of the interface states (in the faceted sample) with enhanced nitrogen incorporation during the POA when the sample surface exposes a higher percentage of (11–20) planes of the SiO<sub>2</sub>/4H-SiC interface.

## Conclusion

In this paper, the electrical activation of the nitrogen incorporated in the SiC near-surface region during low-temperature POA has been demonstrated. Moreover, nanometre-scale crosssectional SCM investigation figured out the depth profile of the activated nitrogen. A correlation between the electrostructural properties of SiO<sub>2</sub>/4H-SiC interfaces and the interface-state density of MOS was established. In particular, irrespective of the different interface roughness, lower values of  $D_{it}$  were found in the faceted sample. The different values of the interface states density can be explained by the peculiar surface morphology of the devices channel region with particular regard to the different nitrogen incorporation through interfaces exposing different ratios between (0001) and (11–20) planes.

## Experimental

Scanning Probe Microscopy (SPM) measurements were carried out by using a Digital Instrument D3100 equipped with the Nanoscope<sup>®</sup> V controller. Local resistance measurements were carried out by using the scanning spreading resistance module (SSRM) [18,19], and cross-sectional local active-doping profiling was carried out employing differential capacitance (dC/dV) imaging with the scanning capacitance module (SCM) [20,21].

The MOS capacitor for the measurements of  $D_{it}$  was fabricated on an n-type 4H-SiC epitaxial layer grown onto heavily doped n<sup>+</sup>-type substrates with a 4° off-axis disorientation towards the <11–20> direction. [22]. A 30 nm thick SiO<sub>2</sub> layer deposited by plasma-enhanced chemical vapour deposition was used as the gate dielectric. After deposition of the gate oxide, a POA annealing at 1150 °C was performed under an N<sub>2</sub>O atmosphere.

MOSFET devices were fabricated on two different surfaces (*flat* and *faceted*). Both samples were subjected to p-type doping by Al ion implantation and to a subsequent high-temperature (1650 °C) postimplantation annealing for dopant activation. On one sample, the SiC surface was coated by a protective carbon capping layer during the annealing, resulting in a smooth morphology. A rough surface formed by facets exposing both the (0001) basal plane and the (11-2n) facets, was obtained for

the second sample annealed without the cap layer. MOS capacitors were fabricated on both wafers [12]. Cross-sectional SCM was performed for carrier-depth profiling under the gate oxide region.

The sample for the selective exposure of 4H-SiC bare surface to the postoxidation annealing (POA) was fabricated as follows: the surface of a p<sup>+</sup>-type 4H-SiC layer was selectively exposed to the same POA process in N<sub>2</sub>O, by using a pattern width of 20  $\mu$ m of exposed substrate separated by 40  $\mu$ m of protected substrate onto a thick SiO<sub>2</sub> hard mask. After removing the hard mask, SSRM was performed on bare 4H-SiC exposed to cleaning, wet-etching in diluted HF, and standard rinsing.

## Acknowledgements

The authors would like to thank S. Di Franco for his support during fabrication of the device prototypes. ST Microelectronics R&D in Catania is acknowledged for funding and invaluable assistance. This work was partially funded by the Marie Curie ITN NetFISiC (EC FP7 grant agreement no. 264613), by the national project PON Ambition Power (PON01\_00700), and by ST Microelectronics, Catania (under the research contract 04.03.2011.002 D.B. Legal Dept. 3774).

#### References

- Ciobanu, F.; Pensl, G.; Afanas'ev, V. V.; Schöner, A. *Mater. Sci. Forum* 2005, 483–485, 693–696.

- doi:10.4028/www.scientific.net/MSF.483-485.693

Afanas'ev, V. V.; Ciobanu, F.; Dimitrijev, S.; Pensl, G.; Stesmans, A. J. Phys.: Condens. Matter 2004. 16. S1839–S1856.

- doi:10.1088/0953-8984/16/17/019

Rozen, J.; Ahyi, A. C.; Zhu, X.; Williams, J. R.; Feldman, L. C.

- IEEE Trans. Electron Devices 2010, 58, 3808–3811.

doi:10.1109/TED.2011.2164800

Wang, Y.; Khan, T.; Koushik Balasubramanian, M.; Naik, H.;

- Wang, Y.; Knan, I.; Kousnik Balasubramanian, M.; Naik, H.; Wang, W.; Chow, T. P. *IEEE Trans. Electron Devices* 2008, 55, 2046–2053. doi:10.1109/TED.2008.926674

- Ryu, S.-H.; Dhar, S.; Haney, S.; Agarwal, A.; Lelis, A.; Geil, B.; Scozzie, C. *Mater. Sci. Forum* **2009**, *615–617*, 743–748. doi:10.4028/www.scientific.net/MSF.615-617.743

- Kosugi, R.; Umeda, T.; Sakuma, Y. Appl. Phys. Lett. 2011, 99, 182111. doi:10.1063/1.3659689

- Umeda, T.; Esaki, K.; Kosugi, R.; Fukuda, K.; Ohshima, T.; Morishita, N.; Isoya, J. *Appl. Phys. Lett.* **2011**, *99*, 142105. doi:10.1063/1.3644156

- Osterman, J.; Hallén, A.; Anand, S. Appl. Phys. Lett. 2002, 81, 3004–3006. doi:10.1063/1.1514829

- Song, X.; Bazin, A. E.; Michaud, J. F.; Cayrel, F.; Zielinski, M.; Portail, M.; Chassagne, T.; Collard, E.; Alquier, D. *Mater. Sci. Forum* **2011**, 679–680, 193–196. doi:10.4028/www.scientific.net/MSF.679-680.193

- Giannazzo, F.; Calcagno, L.; Raineri, V.; Ciampolini, L.; Ciappa, M.; Napolitani, E. *Appl. Phys. Lett.* **2001**, 79, 1211. doi:10.1063/1.1394956

- Giannazzo, F.; Musumeci, P.; Calcagno, L.; Makhtari, A.; Raineri, V. Mater. Sci. Semicond. Process. 2001, 4, 195. doi:10.1016/S1369-8001(00)00129-3

- 12. Frazzetto, A.; Giannazzo, F.; Fiorenza, P.; Raineri, V.; Roccaforte, F. *Appl. Phys. Lett.* **2011**, *99*, 072117. doi:10.1063/1.3627186

- Fiorenza, P.; Giannazzo, F.; Frazzetto, A.; Roccaforte, F. J. Appl. Phys. 2012, 112, 084501. doi:10.1063/1.4759354

- Swanson, L. K.; Fiorenza, P.; Giannazzo, F.; Frazzetto, A.; Roccaforte, F. *Appl. Phys. Lett.* **2012**, *101*, No. 193501. doi:10.1063/1.4766175

- Saitoh, H.; Seki, A.; Manabe, A.; Kimoto, T. Mater. Sci. Forum 2007, 556–557, 659–662. doi:10.4028/www.scientific.net/MSF.556-557.659

- Nakagawa, H.; Tanaka, S.; Suemune, I. Phys. Rev. Lett. 2003, 91, 226107. doi:10.1103/PhysRevLett.91.226107

- Camarda, M.; Severino, A.; Fiorenza, P.; Raineri, V.; Scalese, S.; Bongiorno, C.; La Magna, A.; La Via, F.; Mauceri, M.; Crippa, D. *Mater. Sci. Forum* **2011**, 679–680, 358–361. doi:10.4028/www.scientific.net/MSF.679-680.358

- Eyben, P.; Xu, M.; Duhayon, N.; Clarysse, T.; Callewaert, S.; Vandervorst, W. J. Vac. Sci. Technol., B 2002, 20, 471–478. doi:10.1116/1.1424280

- Giannazzo F; Roccaforte F; Raineri, V. Appl. Phys. Lett. 2007, 91, 202104. doi:10.1063/1.2813022

- Fiorenza, P.; Raineri, V.; Ebbinghaus, S. G.; Lo Nigro, R. CrystEngComm 2011, 13, 3900–3904. doi:10.1039/c0ce00948b

- 21. Fiorenza, P.; Raineri, V.; Ferrarelli, M. C.; Sinclair, D. C.; Lo Nigro, R. *Nanoscale* **2011**, *3*, 1171–1175. doi:10.1039/c0nr00828a

- Schroder, D.K. Semiconductor Material and Device Characterization, 3rd ed.; John Wiley and Sons: Hoboken, New Jersey, 2006. doi:10.1002/0471749095

# License and Terms

This is an Open Access article under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/2.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

The license is subject to the *Beilstein Journal of Nanotechnology* terms and conditions: (http://www.beilstein-journals.org/bjnano)

The definitive version of this article is the electronic one which can be found at: doi:10.3762/bjnano.4.26