Abstract

The recently proposed high–low Kelvin probe force microscopy (KPFM) enables evaluation of the effects of semiconductor interface states with high spatial resolution using high and low AC bias frequencies compared with the cutoff frequency of the carrier transfer between the interface and bulk states. Information on the energy spectrum of the interface state density is important for actual semiconductor device evaluation, and there is a need to develop a method for obtaining such physical quantities. Here, we propose high–low Kelvin probe force spectroscopy (high–low KPFS), an electrostatic force spectroscopy method using high- and low-frequency AC bias voltages to measure the interface state density inside semiconductors. We derive an analytical expression for the electrostatic forces between a tip and a semiconductor sample in the accumulation, depletion, and inversion regions, taking into account the charge transfer between the bulk and interface states in semiconductors. We show that the analysis of electrostatic forces in the depletion region at high- and low-frequency AC bias voltages provides information about the interface state density in the semiconductor bandgap. As a preliminary experiment, high-low KPFS measurements were performed on ion-implanted silicon surfaces to confirm the dependence of the electrostatic force on the frequency of the AC bias voltage and obtain the interface state density.

Introduction

With the recent miniaturization of semiconductor devices, understanding the physical and electrical properties of semiconductor devices, such as the dopant concentration, dopant distribution, and defect level distribution, at the nanoscale has become important. Among the physical properties of semiconductors, information on semiconductor interface states is particularly important. For example, in semiconductor devices such as field-effect transistors, the presence of semiconductor interface states is known to significantly affect device operation characteristics [1-3]. Therefore, direct observation of semiconductor surfaces with nanoscale spatial resolution will become even more important for understanding and controlling the effects of these properties on devices and for evaluating semiconductor device operation.

Kelvin probe force microscopy (KPFM) is known as a method that can measure the contact potential difference (CPD) between a tip and a sample with high spatial resolution [4,5]. KPFM is based on the detection of the electrostatic force between a tip and a sample using atomic force microscopy (AFM) [6-8]. CPD and topographic measurements have been performed on a variety of sample surfaces, including metals [9,10], semiconductors [11-14], and insulators [15-17]. When a semiconductor sample is measured by KPFM, the measured CPD is related to information about the semiconductor properties such as dopant density, surface charge, band bending, and interface state density [18]. In particular, previous studies of silicon substrates with different impurity concentrations measured by KPFM have shown that when the impurity concentration is very high (>1016 cm−3), surface band bending occurs, and the measured CPD approaches that of the intrinsic semiconductor [19]. Thus, since the CPD is strongly affected by the surface properties, accurate evaluation of the surface state and bulk impurity concentration requires a method that extracts only the surface potential effect due to interface states.

Recently, we proposed high–low Kelvin probe force microscopy (high–low KPFM) as a technique to solve the above problem [20,21]. High–low KPFM is a method for measuring the magnitude and direction of band bending due to interface states by applying low-frequency and high-frequency AC bias voltages between the tip and the sample with respect to the cutoff frequency fc of carrier transport between the bulk and interface states and measuring the difference in CPD by KPFM. In high–low KPFM, frequency modulation (FM) KPFM (FM-KPFM) combined with FM-AFM is used to detect the tip–sample interaction force. FM-KPFM has several advantages, namely high sensitivity to the electrostatic force gradient, high detection sensitivity using a cantilever with a weak spring constant at the first resonance, ease of implementation in adding FM-AFM, and no need to enhance the bandwidth of the cantilever deflection sensor. FM-KPFM is used to apply an AC bias voltage at frequencies lower than the cutoff frequency fc of carrier transport, and heterodyne FM-KPFM, based on the heterodyne effect (frequency conversion effect) between mechanical oscillation of the cantilever and electrostatic force oscillation, is used to apply an AC bias voltage at frequencies higher than the cutoff frequency fc of carrier transport. To date, high–low KPFM has successfully visualized the surface band bending of pn-patterned silicon substrates [22]. However, in high–low KPFM, the CPD is compensated by a DC bias voltage. Hence, a certain DC voltage, determined by the CPD, is applied to the semiconductor sample. Therefore, the surface potential of the semiconductor is fixed at a certain energy, and only the surface state near the Fermi level of the surface is reflected in CPD measurements, making measurement of the energy distribution of the interface states within the bandgap difficult. Thus, a method for measuring the energy distribution of the interface states must be developed.

Kelvin probe force spectroscopy (KPFS) or electrostatic force spectroscopy is a technique that enables energy spectroscopy of interface states in the semiconductor bandgap, as described above. Since KPFS does not fix the DC bias voltage but sweeps it over a certain voltage range, it has the advantage of obtaining information on carriers in the energy range corresponding to the swept bias voltage range. For example, the use of electrostatic force spectroscopy to measure the localized energy levels of insulating layers on semiconductor surfaces has been reported to be feasible [22]. Therefore, we can expect that the KPFS method described above can be combined with high–low KPFM to measure the energy distribution of the interface states.

In this study, we propose high-low KPFS using high- and low-frequency AC bias voltages to measure the interface state density inside semiconductors. We derive an analytical expression for the electrostatic force between the tip and the sample that takes into account the charge transfer between the bulk and interface states in the semiconductor. We show that the electrostatic force between the tip and the semiconductor sample strongly depends on the capacitance of the charge depletion region on the surface, and that the analysis of the electrostatic force at low- and high-frequency AC bias voltages can provide information on the interface state density in the semiconductor bandgap. We also demonstrate using a pn-patterned silicon substrate that the interface state density can be measured.

Theory

To understand the principle of the high–low KPFS proposed in this study, we discuss the electrostatic forces acting between the tip and the sample when high- and low-frequency AC bias voltages are applied. The tip and the sample are assumed to be metallic and semiconducting, respectively, and a metal–insulator–semiconductor (MIS) structure consisting of the metallic tip, a vacuum gap, and the semiconducting sample is considered (Figure 1a). No oxide film on the semiconductor surface is assumed, and to simplify the discussion, the CPD between the tip and the semiconductor substrate is assumed to be zero.

![[2190-4286-14-18-1]](/bjnano/content/figures/2190-4286-14-18-1.png?scale=2.0&max-width=1024&background=FFFFFF)

Figure 1: (a) Schematic of the metal tip–gap–semiconductor sample. (b) Energy band diagram of the metal–gap–semiconductor sample. Emission and capture of carriers (electrons and holes) occur between the interface and bulk states of the semiconductor sample when a low-frequency AC bias voltage is applied.

Figure 1: (a) Schematic of the metal tip–gap–semiconductor sample. (b) Energy band diagram of the metal–gap–s...

To investigate the electrostatic force acting between the tip and the semiconductor surface, we use the theoretical model reported by Hudlet and co-workers [23]. For simplicity, let us assume that the tip and the sample are represented by parallel plate capacitors. In this case, the electrostatic force Fele acting between the tip and the semiconductor surface is expressed as

where Q is the charge per unit surface area induced on the semiconductor surface and ε0 is the dielectric constant of vacuum.

A bias voltage Vdc + Vac·cos 2πft is applied between the tip and the semiconductor sample, where Vdc, Vac, and f are the DC bias voltage, amplitude of the AC bias voltage, and modulation frequency of the AC bias voltage, respectively. The modulated electrostatic force Fele(f) between the tip and the surface is expressed as follows using Taylor series expansion:

where Vs is the surface potential of the semiconductor sample.

Next, we consider the charge Q induced on the semiconductor surface. When a bias voltage is applied between a metal tip and a semiconductor surface, a surface potential is generated on the semiconductor surface, resulting in, for example, surface charge accumulation, depletion, and inversion states. The relationship between this surface charge and the electrostatic force between the tip and the sample has already been discussed by Hudlet and co-workers [23]. Additionally, there are interface states on the semiconductor surface. Therefore, the contribution of these interface states to the AC component of the electrostatic force must be considered. When an AC bias voltage is applied between the tip and the sample, the bulk Fermi level does not change on the semiconductor side, whereas the interface states move up and down with the conduction and valence bands. This causes capture of carriers (electrons and/or holes) from the bulk side by the interface states and, conversely, emission of carriers from the interface states to the bulk side, which contribute to the electrostatic force (Figure 1b). Therefore, the total charge Q induced on the semiconductor surface by the voltage application is given by the sum of the charge Qs due to the surface potential Vs and the charge Qit due to the interface states as follows:

Here, we consider the charge Qs due to the surface potential Vs. In the case of an n-type semiconductor, the charge Qs as a function of the surface potential Vs is expressed as follows [23,24]:

where ND is the dopant density, ni is the intrinsic carrier density, and ε is the dielectric constant. LD is the Debye length for majority carriers (electrons), which characterizes the change in the potential inside the semiconductor. kB, T and e are the Boltzmann constant, absolute temperature, and elementary charge (e > 0), respectively.

Since the applied voltage V is divided between the semiconductor and the gap, the following equation is obtained:

where Cg is the capacitance per unit surface area due to the gap between the tip and the surface. The charge Qs due to the surface potential Vs is obtained by numerically solving Equations 4–8.

When a positive or negative bias voltage is applied to the MIS structure consisting of the metal tip, gap, and semiconductor sample, three cases exist at the semiconductor surface. For an n-type semiconductor, when a positive bias voltage is applied to the metal tip (Vdc > 0), electrons (majority carriers) in the semiconductor are attracted to the surface, forming an accumulation layer of electrons. When a small negative bias voltage is applied to the metal tip (Vdc < 0), electrons (majority carriers) in the semiconductor are depleted from the surface, forming a depletion layer. When a large negative bias voltage is applied to the metal tip, the number of holes (minority carriers) is greater than that of electrons at the surface, and holes are induced in the semiconductor at the surface, forming an inversion layer of holes.

Here, in the accumulation region, since and exp(u) ≫ |u + 1|, Qs is dominated by the first term in Equation 5 and is given by [23,24]

In the depletion region, Qs is dominated by the second term −u in the square brackets on the right-hand side of Equation 5 and is given by

In the strong inversion region, Qs is dominated by the fourth term in the square brackets on the right-hand side of Equation 5 and is given by

Similar results can be obtained for a p-type semiconductor.

Next, we consider the charge Qit due to the interface states. In indirect-bandgap semiconductors such as Si with a low carrier density below 1017 cm−3, the charge (electron and hole) transfer between the interface and bulk states at low carrier density can be explained by the model with Shockley–Read–Hall (SRH) statistics [25,26]. This model is based on the charge capture and emission between the interface and bulk states (Figure 2). Assume that and

are the capture rates for electrons and holes per electron and hole, respectively, when all interface states are unoccupied, and

and

are the emission rates for electrons and holes per electron and hole, respectively. The capture rates per unit volume for electrons and holes (

and

) are given by [25,26]

where fit is the fraction of occupied interface states. n and p are the electron and hole densities of the bulk state. Analogously, the emission rates per unit volume for electrons and holes ( and

) are given by

In thermal equilibrium, the amount of capture and the amount of emission for a carrier coincide as follows:

![[2190-4286-14-18-2]](/bjnano/content/figures/2190-4286-14-18-2.png?scale=2.0&max-width=1024&background=FFFFFF)

Figure 2: Schematic model of carrier emission and capture between the interface and bulk states of the semiconductor sample.

Figure 2: Schematic model of carrier emission and capture between the interface and bulk states of the semico...

The net generation/recombination rate RSRH is given by the following equation [25,26]:

with

The index 0 indicates equilibrium quantities. For low-level injection, at which the excess minority carrier density is low compared to the equilibrium majority carrier density, the net generation/recombination rate RSRH is dominated by the hole (minority carrier) lifetime τp in n-type semiconductors and the electron (minority carrier) lifetime τn in p-type semiconductors as follows:

where σn and σp are the capture cross sections for electrons and holes, respectively, vth is the thermal velocity, and Nit is the concentration of interface states. These equations indicate that the carrier lifetimes τp and τn are reciprocals of the capture rates per single carrier determined by the capture cross sections σn and σp, thermal velocity vth, and concentration of interface states Nit, which depend on semiconductor type, temperature, carrier density, and interface state density.

For an n-type Si semiconductor at room temperature, the hole (minority carrier) lifetime τp as a function of electron (majority carrier) density n has been experimentally investigated and is reported to be less than 2.5 × 10−5 s for low carrier densities n < 5 × 1017 cm−3 [26]. Additionally, for metal-oxide semiconductor capacitors on Si(100) substrates, the lifetimes τn and τp as functions of the sum of the surface potential and the Fermi potential with respect to the midgap have been experimentally investigated [24]. As a result, for Si semiconductors with a low carrier density (small Fermi potential), the lifetime has been reported to be less than 5 × 10−6 s. These results indicate that the cutoff frequency fc of carrier transport between the interface and bulk states for a Si substrate with a low carrier density is approximately 200 kHz. Therefore, when an AC bias voltage with a frequency higher than this cutoff frequency fc is applied between the tip and the Si semiconductor sample, the charge Qit caused by the interface states cannot respond to changes in the surface potential. In contrast, when an AC bias voltage with a frequency much lower than fc is applied between the tip and the Si semiconductor sample, the charge Qit can respond to changes in the surface potential.

Low KPFS

First, we consider the case in which the frequency of the AC bias voltage is lower than the cutoff frequency fc of the carrier transport between the interface and bulk states. The AC bias voltage Vac·cos 2πfmt is applied between the tip and the surface, where fm is the modulation frequency of the AC bias voltage. Since the charge Qit due to interface states can follow the change in the surface potential, dQ/dVs and dVs/dV can be expressed as

where CD and Cit are the capacitance per unit surface area due to the depletion layer of the semiconductor and the capacitance due to the interface charge, respectively. The applied voltage is divided between the semiconductor and the gap, and the following equation is obtained:

Therefore, the modulation frequency fm component of the electrostatic force Fele(fm) acting on the probe is expressed as

where CLF is the low-frequency tip–sample capacitance. The equivalent circuit for this capacitance CLF is shown in Figure 3b. Note that this equivalent circuit is equal to the equivalent circuit of the impedance model (SRH model) of the MIS structure (Figure 3a), neglecting the resistance component Rit. This result suggests a similarity between conventional impedance measurements and electrostatic force measurements in semiconductor surface and interface evaluation techniques.

![[2190-4286-14-18-3]](/bjnano/content/figures/2190-4286-14-18-3.png?scale=2.0&max-width=1024&background=FFFFFF)

Figure 3: (a) Equivalent circuit of the impedance model (SRH model) of the MIS structure. (b) Equivalent circuit of tip–sample capacitance CLF in low-frequency KPFS with a low-frequency AC bias voltage. (c) Equivalent circuit of tip–sample capacitance CHF in high-frequency KPFS with a high-frequency AC bias voltage. Cg: capacitance due to the tip–surface gap; CD: capacitance due to the depletion layer; Cit: capacitance due to interface states; Rit: resistance due to interface states.

Figure 3: (a) Equivalent circuit of the impedance model (SRH model) of the MIS structure. (b) Equivalent circ...

The average distance between the tip and the sample is zto, and the amplitude and frequency of the vibrating cantilever are A and f0, respectively. The time-varying tip–sample distance is given by

From this equation and the relationship Cg = ε0/z, we obtain the following expression:

Because of frequency mixing between the electrostatic force due to the AC bias voltage cos 2πfmt and the cantilever vibration cos 2πf0t, f0 ± fm components of the electrostatic force Fele,L(f0 ± fm) appear:

When the electrostatic force is detected by the FM method, the electrostatic force Fele,L(f0 ± fm) is demodulated into the fm component of the frequency shift ΔfL(fm), which is expressed as

where k is the spring constant of the cantilever. This equation indicates that the slope of the dependence of the fm component of the frequency shift ΔfL(fm) on the DC bias voltage Vdc (ΔfL(fm)–Vdc curve) is proportional to the capacitance inside the semiconductor at a low-frequency AC bias (CD + Cit).

High KPFS

Next, we consider the case in which the frequency of the AC bias voltage is higher than the cutoff frequency fc of the carrier transport between the interface and bulk states. We assume that the heterodyne FM method [21] is used and that an AC bias voltage with a high frequency near twice the vibration frequency of the cantilever Vac·cos 2π(2f0 + fm)t is applied (that is, f = 2f0 + fm). In the high-frequency case, the contribution from the interface charge Qit due to interface states cannot follow the change in surface potential Vs, so this contribution can be neglected. Therefore, dQ/dVs and dVs/ dV can be expressed as

Since the applied voltage is divided between the semiconductor and the gap, the following equation is obtained:

Therefore, the modulation frequency (2f0 + fm) component of the electrostatic force Fele(2f0 + fm) acting on the tip is expressed as

where CHF is the high-frequency tip–sample capacitance. The equivalent circuit for this capacitance CHF is shown in Figure 3c. Note that this equivalent circuit is equal to the equivalent circuit of the impedance of the MIS structure derived from the SRH model (Figure 3a), neglecting the capacitance component Cit and resistance component Rit due to the semiconductor interface states.

Now, the capacitance CD of the depletion layer of the MIS structure is given by CD = |dQs/dVs|. In the charge accumulation region, from Equation 9, CD is given by

In the depletion region, from Equation 10, CD is given by

In the inversion region, from Equation 11, CD is given by

Therefore, in the depletion region, we can obtain the following expression:

In the accumulation and inversion regions, we can obtain the following expression:

Because of frequency mixing between the electrostatic force due to the AC bias voltage cos 2π(2f0 + fm)t and the cantilever vibration cos2πf0t, the f0 + fm component of the electrostatic force Fele,H(f0 + fm) appears:

- In the depletion region,

- In the accumulation and inversion regions,

In the FM method, the electrostatic force Fele,H(f0 + fm) is demodulated into the fm component of the frequency shift ΔfH(fm). The resulting fm component of the frequency shift ΔfH(fm) is expressed in the depletion region as

and in the accumulation and inversion regions as

In the above equations, the slope of the dependence of the fm component of the frequency shift ΔfH(fm) on Vdc (ΔfH(fm)–Vdc curve) is proportional to the capacitance CD inside the semiconductor in the depletion region and to the gap capacitance Cg in the accumulation and inversion regions. Note that at a high-frequency AC bias voltage, as shown in Equation 43 and Equation 44, only the f0 + fm component of the electrostatic force Fele,H(f0 + fm) is demodulated, while at a low-frequency AC bias voltage, as shown in Equation 30, the f0 + fm and f0 − fm components of the electrostatic force Fele,L(f0 ± fm) are demodulated. Therefore, the coefficients in Equation 43 and Equation 44 are 1/2 of those in Equation 30.

High–low KPFM

Here, we consider the derivation of the surface potential Vs induced by the interface states. When the KPFM measurement is performed using a low-frequency AC bias voltage, the DC bias voltage that makes the modulation component of the frequency shift ΔfL(fm) zero is

Here, Vs(LF) can be thought of as reflecting information about the sum of the surface potential (band bending) due to the interface states and the CPD between the metal tip and the bulk state of the sample. This is because when a low-frequency AC bias voltage is used, the charge Qit can respond to changes in the surface potential. In contrast, when the KPFM measurement is performed using a high-frequency AC bias voltage, the DC bias voltage that makes the modulation component of the frequency shift ΔfH(fm) zero is

Here, Vs(HF) can be thought of as reflecting information about the CPD between the metal tip and the bulk state of the sample. This is because when a high-frequency AC bias voltage is used, the charge Qit caused by the interface states cannot respond to changes in the surface potential. Therefore, as shown in the next equation, high–low KPFM, which measures the difference between Vs(LF) with a low-frequency AC bias voltage and Vs(HF) with a high-frequency AC bias voltage, reflects the information of the surface potential (band bending) due to the interface states [21,22].

Regarding the selection of ±, + is for applying a bias voltage to the sample and − is for applying a bias voltage to the tip. The + and − signs of ΔVs indicate upward and downward band bending at the interface, respectively.

High–low KPFS

Next, let us consider the derivation of the interface state density Dit from Equation 30 and Equation 43, which relate the modulation components of the frequency shift to the AC bias voltage at low and high frequencies. In the case of a low-frequency AC bias, from Equation 30, the slope of the ΔfL(fm)–Vdc curve is proportional to the low-frequency capacitance inside the semiconductor (CD + Cit). In the case of a high-frequency AC bias, from Equation 43, twice the slope of the ΔfH(fm)–Vdc curve in the depletion region is proportional to the high-frequency capacitance within the semiconductor (CD ). Using these relationships, the interface state density Dit at each DC bias voltage Vdc can be obtained by taking the difference in the slope of the dependence of Δf(fm) on the DC bias voltage for low and high frequencies (the capacitance Cit due to the interface charge) [24] as follows:

Δf–Vdc curve with low- and high-frequency AC bias voltages

We consider the derivation of the Δf–Vdc curve. The DC electrostatic force Fele(0) between the tip and the surface when using an AC bias voltage with frequency f (= fm or 2f0 + fm) is expressed as follows using Taylor series expansion up to the second-order terms:

The contribution of the second-order terms of the Taylor series expansion of the electrostatic force is much smaller than that of the zeroth-order term and can be ignored. Qs can be obtained by solving Equations 4–8 numerically, but the relationship between the DC bias voltage Vdc and the frequency shift Δf cannot be understood analytically.

Therefore, assuming that the vibration amplitude of the cantilever is very small compared to the length of the electrostatic force interaction region, we can obtain the analytical relationship between Vdc and the frequency shift Δf. The gradient of the electrostatic force is given by

From Equations 24 and 33 and the relationship Cg = ε0/z, dVs/dz is given by

and

for low- and high-frequency AC bias voltages, respectively. From Equations 22, 24, 31, and 33, the frequency shift of the electrostatic force is given by

and

for low- and high-frequency AC bias voltages, respectively. As shown in Equations 36–38, CD in the charge depletion region is very different from CD in the charge accumulation and charge inversion regions. Thus, these equations suggest that the ΔfL–Vdc curve for a low-frequency AC bias voltage is almost parabolic with respect to Vdc when CD < Cit, while the ΔfH–Vdc curve for a high-frequency AC bias voltage is divided into three regions with respect to Vdc. These analytical equations do not necessarily quantitatively agree with the experimental results because they approximate small cantilever vibration amplitudes, but they can qualitatively explain the behavior of Δf–Vdc curves.

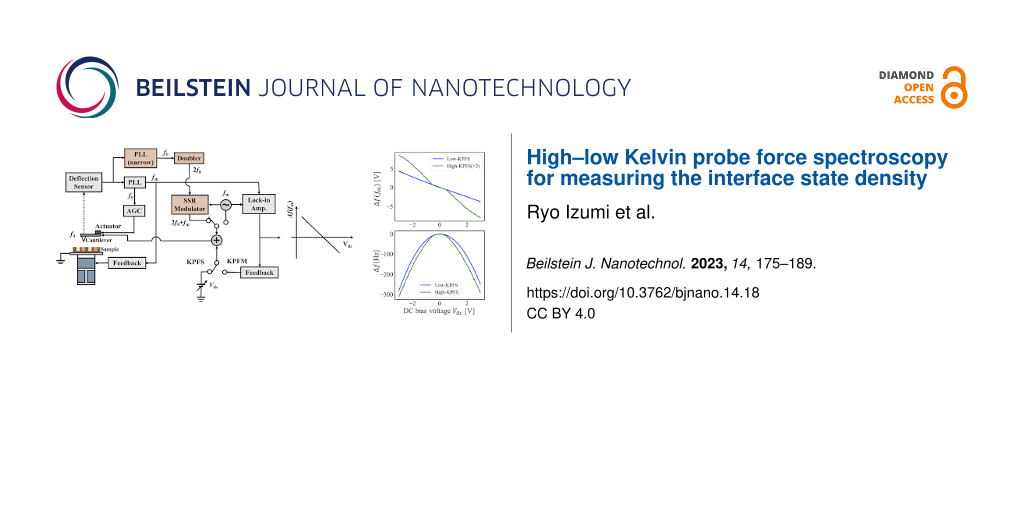

Experimental

Figure 4 shows the block diagram of AFM and high–low KPFS using AC bias voltages with high and low frequencies. The FM method was used to detect the tip–sample interaction force. The cantilever displacement signal measured using the displacement detection system was controlled by an automatic gain control (AGC) circuit to keep the cantilever vibration amplitude A constant, and the frequency shift Δf of the cantilever was measured using a phase-locked loop (PLL) circuit (SPECS GmbH: Nanonis OC4). AFM measurements were performed by controlling the tip–sample distance so that the frequency shift of the cantilever (Δfset) was constant. In the low KPFS measurement using a low-frequency AC bias, the AC bias voltage Vac·cos 2πfmt was generated by an oscillator. In contrast, in the high KPFS measurement using a high-frequency AC bias voltage, the signal cos 2π(2f0)t, which is a signal of twice the frequency synchronized with the cantilever vibration signal cos 2πf0t, was generated by a PLL circuit with a narrow bandwidth and a doubler (amplitude modulator for second-harmonic generation) (Zurich Instruments: HF2LI-PLL and HF2LI-MOD). By mixing this signal and the signal from the oscillator cos 2πfmt in a single-sideband (SSB) modulator (Zurich Instruments: HF2LI-MOD), the AC bias signal Vac·cos 2π(2f0 + fm)t was generated. The bias voltage, which is the sum of the DC bias voltage Vdc and the AC bias voltage (Vac·cos 2πfmt or Vac·cos 2π(2f0 + fm)t), was applied to the tip, and the ground was connected to the sample. The modulation component of the frequency shift of the cantilever Δf(fm) was detected using a lock-in amplifier (Zurich Instruments: HF2LI). Bias spectral data were obtained by measuring Δf(fm) and Δf as a function of the DC bias voltage Vdc while keeping the distance between the tip and the sample constant. These experiments were performed in a vacuum environment using a JEOL scanning probe microscope (JEOL: JSPM-4210).

![[2190-4286-14-18-4]](/bjnano/content/figures/2190-4286-14-18-4.png?scale=2.0&max-width=1024&background=FFFFFF)

Figure 4: Block diagram of AFM and high–low KPFS. In low KPFS, a signal Vac·cos 2πfmt is generated by the oscillator. In high KPFS, a signal cos 2π(2f0)t of twice the resonance frequency synchronized with the cantilever oscillation is generated by the PLL and the doubler, and a signal Vac·cos 2π(2f0 + fm)t is generated by mixing the signal cos 2π(2f0)t and the signal cos 2πfmt in the SSB modulator. The figure was adapted from [20] (© 2020 Y. Sugawara et al., published by IOP Publishing Ltd., distributed under the terms of the Creative Commons Attribution 4.0 International License, https://creativecommons.org/licenses/by/4.0)

Figure 4: Block diagram of AFM and high–low KPFS. In low KPFS, a signal Vac·cos 2πfmt is generated by the osc...

A silicon substrate patterned with n- and p-type impurities was used as a semiconductor sample [22,27,28]. Figure 5 shows the dopant pattern of the silicon substrate used in the measurements and the impurity concentrations. As shown in Figure 5, the silicon substrate has three types of impurity regions: an n-type region, a p-type region, and an n+-type region. The impurity concentrations of the n, p, and n+ regions are 1 × 1015 cm−3, 2 × 1016 cm−3, and 5 × 1019 cm−3, respectively.

![[2190-4286-14-18-5]](/bjnano/content/figures/2190-4286-14-18-5.png?scale=2.0&max-width=1024&background=FFFFFF)

Figure 5: Schematic of the silicon substrate with three types of impurity pattern, that is, n-, p-, and, n+-type regions, used for the measurement.

Figure 5: Schematic of the silicon substrate with three types of impurity pattern, that is, n-, p-, and, n+-t...

As a force sensor, a PtIr-coated conductive cantilever (NanoWorld: NCHPt) was used. The resonance frequency f0, force constant k, and Q of the PtIr-coated cantilever were 292.68 kHz, 42 N/m, and 8406, respectively.

The cantilever oscillation amplitude for the high–low KPFS measurement was set to A = 10 nm throughout the experiment. The AC bias voltage was Vac = 0.5 V, and the modulation frequencies of the AC bias voltage in high KPFS and low KPFS were 2f0 + fm = 542.3 kHz and fm = 100 Hz, respectively.

Results and Discussion

First, we performed AFM/KPFM measurements on the pn-patterned Si surface to identify the dopant regions on the semiconductor surface. Figure 6a and Figure 6b show the topographic and CPD images of the pn-patterned Si substrate, respectively. The CPD image in Figure 6b was obtained by KPFM using an AC bias voltage with a low modulation frequency of fm = 100 Hz. Figure 6c and Figure 6d show the line profiles corresponding to the white lines in Figure 6a and Figure 6b, respectively. From the topographic image and the line profile, there are rodlike protrusions on the surface with a width of approximately 1 μm and a height of approximately 60 nm. Compared with the data of the pn-patterned Si substrate in Figure 5, these rodlike protrusions correspond to p-type or n-type regions, and the low areas between the rodlike protrusions correspond to n+-type regions. From the CPD image and the line profile, there is a difference of approximately 30–40 mV between the CPD values of the two rodlike protrusions; the region with the highest CPD value is the p-type region, the region with a CPD value 30–40 mV below the highest value is the n-type region, and the region with the lowest CPD value is the n+-type region. From these CPD values, the n+-, n-, and p-type regions can be assigned as shown in Figure 6d [22,27,28].

![[2190-4286-14-18-6]](/bjnano/content/figures/2190-4286-14-18-6.png?scale=2.0&max-width=1024&background=FFFFFF)

Figure 6: (a) Surface topography and (b) CPD image of the pn-patterned Si surface. The CPD image was obtained by KPFM using an AC bias voltage with a low modulation frequency of fm = 100 Hz. The scan size was 7 μm × 2.1 μm. (c) Line profile corresponding to the white line in panel (a); (d) line profile corresponding to the white line in panel (b).

Figure 6: (a) Surface topography and (b) CPD image of the pn-patterned Si surface. The CPD image was obtained...

Next, we performed high–low KPFS experiments at the center point in the n-type region shown in Figure 6a. Figure 7a shows the dependence of the modulation component of the frequency shift Δf(fm) on the DC bias voltage Vdc in high–low KPFS (Δf(fm)–Vdc curves). Since the coefficients in Equations 43 and 44 for high KPFS are 1/2 compared with those in Equation 30 for low KPFS, the modulation component of the frequency shift Δf(fm) in high KPFS is doubled. The tip–sample distance was fixed at Δfset = −300 Hz (zto ≈ 15 nm) as the frequency shift set point when the DC bias voltage Vdc = 3 V and the AC bias voltage with amplitude Vac = 0.5 V were applied. In low KPFS, the Δf(fm)–Vdc curve shows an almost linear behavior with respect to Vdc from −3.5 V to +3.5 V. In contrast, in high KPFS, the Δf(fm)–Vdc curve does not show a linear behavior with respect to Vdc and is roughly divided into three regions: (i) −3.5 V to −0.5 V, (ii) −0.5 V to +0.5 V, and (iii) +0.5 V to +3.5 V. The slope of the curve is larger in regions (i) and (iii) and smaller in region (ii). These experimental results on the Δf(fm)–Vdc curves in Figure 7a agree well with the theoretical expectation that the ΔfL(fm)–Vdc curve for low-frequency AC bias voltages is nearly linear with respect to Vdc with slope CD + Cit and that the ΔfH(fm)–Vdc curve for high-frequency AC bias voltages is divided into three regions with respect to Vdc with slopes of CD in the charge depletion region and of Cg in the charge accumulation and charge inversion regions. A similar result that the Δf(fm)–Vdc curve is divided into three regions has already been observed in organic semiconductor samples by Schumacher and co-workers [29].

![[2190-4286-14-18-7]](/bjnano/content/figures/2190-4286-14-18-7.png?scale=2.0&max-width=1024&background=FFFFFF)

Figure 7: (a) Δf(fm)–Vdc curves and (b) Δf–Vdc curves obtained on the n-type Si surface. The tip–sample distance was set with Δfset = −300 Hz (zto ≈ 15 nm) when Vdc = 3 V and Vac = 0.5 V were applied between the tip and the sample.

Figure 7: (a) Δf(fm)–Vdc curves and (b) Δf–Vdc curves obtained on the n-type Si surface. The tip–sample dista...

The DC bias voltages that reduced Δf(fm) to zero are slightly different depending on the frequency of the AC bias voltage: Vs(LF) ≈ 47.5 mV and Vs(HF) ≈ 12.0 mV for low- and high-frequency AC bias voltages, respectively. The difference between Vs(LF) and Vs(HF) is ΔVs = −35.5 mV, which indicates that the interface band is bent downward in the n-type region, suggesting the presence of donor-like interface states [22].

Figure 7b shows the dependence of the frequency shift Δf on DC bias voltage Vdc in high–low KPFS (Δf–Vdc curves) simultaneously measured with Figure 7a. The Δf–Vdc curve is almost parabolic for the low-frequency AC bias voltage. In contrast, the Δf–Vdc curve for the high-frequency AC bias voltage is highly distorted from parabolic, especially in the Vdc range of −3.5 V to −0.5 V (the charge accumulation region) and +0.5 V to +3.5 V (the charge inversion region). These experimental results on the Δf–Vdc curves in Figure 7b also agree well with the theoretical expectation that the Δf–Vdc curve is almost parabolic for low-frequency AC bias voltages, while it is divided into three regions with respect to Vdc for high-frequency AC bias voltages.

This is the first observation of the phenomenon in which the Δf(fm)–Vdc and Δf–Vdc curves are highly dependent on the frequency of the applied AC bias voltage. These results experimentally show that carrier transport between the bulk and interface states of a semiconductor sample is strongly affected by the frequency of the AC bias voltage and that there is indeed a difference between the low-frequency tip–sample capacitance (CLF) and the high-frequency tip–sample capacitance (CHF).

Next, we performed high–low KPFS measurements at the same measurement points as in Figure 7, varying the tip–sample distance. Figure 8a and Figure 8b show the measured Δf(fm)–Vdc curves when the tip–sample distance was fixed with Δfset = −200 Hz (zto ≈ 23 nm) and Δfset = −100 Hz (zto ≈ 40 nm), respectively, as the frequency shift set point. The DC bias voltage Vdc = 3 V and the AC bias voltage Vac = 0.5 V were the same as those used in the case of Figure 7. The modulation component of the frequency shift Δf(fm) in high KPFS was doubled. Similarly, Figure 8c and Figure 8d show the Δf–Vdc curves at Δfset = −200 Hz (zto ≈ 23 nm) and Δfset = −100 Hz (zto ≈ 40 nm) simultaneously measured with Figure 8a and Figure 8b, respectively.

![[2190-4286-14-18-8]](/bjnano/content/figures/2190-4286-14-18-8.png?scale=2.0&max-width=1024&background=FFFFFF)

Figure 8: Δf(fm)–Vdc curves obtained on the n-type Si surface at (a) Δfset = −200 Hz and (b) Δfset = −100 Hz. Δf–Vdc curves obtained on the n-type Si surface at (c) Δfset = −200 Hz and (d) Δfset = −100 Hz.

Figure 8: Δf(fm)–Vdc curves obtained on the n-type Si surface at (a) Δfset = −200 Hz and (b) Δfset = −100 Hz....

The Δf(fm)–Vdc curves in low KPFS show an almost linear behavior at both tip–sample distances. In contrast, the Δf(fm)–Vdc curves in high KPFS do not show a linear behavior and are roughly divided into three regions. The Δf(fm)–Vdc curves in high KPFS show that the DC bias voltage region (ii) corresponding to the charge depletion region becomes wider from −1.5 V to +1.5 V (Figure 8a) and from −3.3 V to +3.3 V (Figure 8b) as the tip–sample distance increases. The wider voltage region (ii) is due to the smaller ratio of the DC bias voltage divided inside the semiconductor. Furthermore, as the tip–sample distance increases, the Δf–Vdc curves become nearly parabolic not only for low-frequency AC bias voltages but also for high-frequency AC bias voltages. The reason why the Δf–Vdc curve for high-frequency AC bias voltages becomes almost parabolic as the tip–sample distance increases is because the range of the DC bias voltage corresponding to the charge depletion region is extended.

We also performed high–low KPFS measurements at the center point in the p-type region in Figure 6a. Figure 9a and Figure 9b show the measured Δf(fm)–Vdc curves and Δf–Vdc curves, respectively. The tip–sample distance was fixed with Δfset = −200 Hz (zto ≈ 23 nm) as the frequency shift set point when the DC bias voltage Vdc = 3 V and the AC bias voltage with amplitude Vac = 0.5 V were applied. In Figure 9a, the Δf(fm)–Vdc curve in low KPFS shows an almost linear behavior from −3.5 V to +3.5 V, while the Δf(fm)–Vdc curve in high KPFS is roughly divided into three regions: (i) −3.5 V to −1.5 V, (ii) −1.5 V to +1.5 V, and (iii) +1.5 V to +3.5 V. The slope of the curve is larger in regions (i) and (iii) and smaller in region (ii). The DC bias voltages that reduced Δf(fm) to zero were estimated to be Vs(LF) ≈ 169.4 mV and Vs(HF) ≈ 143.3 mV for low- and high-frequency AC bias voltages, respectively. The difference between Vs(LF) and Vs(HF) is ΔVs = −25.1 mV. This indicates that the interface band is bent downward in the p-type region, consistent with the previous high–low KPFM results [22].

![[2190-4286-14-18-9]](/bjnano/content/figures/2190-4286-14-18-9.png?scale=2.0&max-width=1024&background=FFFFFF)

Figure 9: (a) Δf(fm)–Vdc curves and (b) Δf–Vdc curves obtained on the p-type Si surface. The tip–sample distance was set with Δfset = −200 Hz (zto ≈ 23 nm) when Vdc = 3 V and Vac = 0.5 V were applied between the tip and the sample.

Figure 9: (a) Δf(fm)–Vdc curves and (b) Δf–Vdc curves obtained on the p-type Si surface. The tip–sample dista...

Furthermore, in Figure 9b, the Δf–Vdc curve is almost parabolic for the low-frequency AC bias voltage, whereas it is highly distorted from parabolic for the high-frequency AC bias voltage. Thus, the Δf(fm)–Vdc and Δf–Vdc curves measured in the p-type region are highly dependent on the frequency of the applied AC bias voltage, which is in good agreement with those measured in the n-type region as well as the theoretical prediction.

The dependence of the Δf(fm)–Vdc and Δf–Vdc curves on the frequency of the AC bias voltage is due to the dependence on the contribution of the capacitance Cit caused by the interface states to the electrostatic force. In other words, when a low-frequency AC bias is used, the capacitance inside the semiconductor is given by the sum of the depletion layer capacitance CD and the capacitance Cit due to the interface states according to Equation 30. In contrast, when a high-frequency AC bias is used, the depletion layer capacitance CD or the gap capacitance Cg has a significant effect on the electrostatic force because the capacitance Cit due to the interface states makes no contribution to the electrostatic force according to Equations 43 and 44.

Finally, we estimated the interface state density Dit in the n-type region on the pn-patterned Si surface using the measured Δf(fm)–Vdc curve in Figure 7a for the closest distance between the tip and the surface. In depletion region (ii), the slope of the Δf(fm)–Vdc curve in low KPFS is slightly larger than that in high KPFS. From Equations 30 and 43, at Vdc = −0.3 V, the capacitances per unit area inside the semiconductor were estimated to be CD + Cit ≃ 3.41 × 10−23 F/cm2 in low KPFS and CD ≃ 2.94 × 10−23 F/cm2 in high KPFS. The parameters used in the estimations of the interface state density were the same as those used in the experiments (f0 = 292.68 kHz, k = 42 N/m, and Vac = 0.5 V). The average distance between the tip and the surface was assumed to be zt0 ≃ 15 nm. Hence, the capacitance per unit area due to the surface states was estimated to be Cit ≃ 4.67 × 10−24 F/cm2. From Equation 48, the interface state density was calculated to be Dit ≃ 1.82 × 1014 cm−2 eV at Vdc = −0.3 V. This value is reasonable for the interface state density on the pn-patterned Si surface. This is the first estimate of the interface state density using the high–low KPFS method and demonstrates the usefulness of high–low KPFS.

Conclusion

In this study, we proposed high-low KPFS using high-frequency and low-frequency AC bias voltages to measure the interface state density in semiconductors. We derived an analytical expression for the electrostatic force between the tip and the sample that takes into account the charge transfer between the bulk and interface states in the semiconductor. From the analytical equation, we found that the slopes of the Δf(fm)–Vdc curves for low- and high-frequency AC bias voltages depend on the capacitances CD + Cit and CD between the tip and the sample, respectively. We also showed that the analysis of the difference between CD + Cit and CD for low- and high-frequency AC bias voltages provides information on the interface state density Dit in the semiconductor bandgap.

Experimentally, Δf(fm)–Vdc and Δf–Vdc curves were measured for impurity-doped Si samples (n- and p-types). When a low-frequency AC bias voltage was used, the Δf(fm)–Vdc curves were almost linear, and the Δf–Vdc curves were almost parabolic. In contrast, when a high-frequency AC bias voltage was used, the Δf(fm)–Vdc curves were not linear but roughly divided into three regions, and the Δf–Vdc curves were distorted from a parabolic shape. These differences were due to the dependence on the contribution of the capacitance Cit caused by the interface states to the electrostatic force. That is, when a low-frequency AC bias voltage is used, the capacitance inside the semiconductor is given by the sum of the capacitance Cit caused by the interface states and the depletion layer capacitance CD. In contrast, when a high-frequency AC bias is used, the contribution of the capacitance Cit due to the interface states is almost negligible, and the depletion layer capacitance CD has a large influence on the electrostatic force. In the depletion region, the slope of the Δf(fm)–Vdc curve for a low-frequency AC bias was found to be slightly larger than that for a high-frequency AC bias. We demonstrated for the first time that the interface state density Dit could be estimated from the difference in these slopes.

The experimental result that the Δf–Vdc curves highly depend on the frequency of the applied AC bias voltage strongly suggests the feasibility of a new spectroscopy method to measure the frequency dependence of carrier transfer in a sample. That is, in this high-low KPFS, only fm or 2f0 + fm was used as the frequency of the AC bias voltage, but AC bias voltages with frequencies other than these can be applied to measure Δf–Vdc curves. Therefore, note that the measurement of the Δf–Vdc curve can be applied for AC bias voltages with very high frequencies, such as in the microwave region, which are not applicable in the conventional KPFM and KPFS.

In the future, high–low KPFS measurements with 2D scanning of the tip on the sample surface are expected to enable measurement of the local interface state density of the sample surface on the nanoscale. Therefore, the high–low KPFS method proposed in this study is expected to be widely used for sensitive and high-resolution nanoscale measurements of impurity concentration and defect level distributions at the surfaces and interfaces of various semiconductor materials and devices.

References

-

Reed, M. L.; Plummer, J. D. J. Appl. Phys. 1988, 63, 5776–5793. doi:10.1063/1.340317

Return to citation in text: [1] -

Engel-Herbert, R.; Hwang, Y.; Stemmer, S. J. Appl. Phys. 2010, 108, 124101. doi:10.1063/1.3520431

Return to citation in text: [1] -

Guo, Y.; Wei, X.; Shu, J.; Liu, B.; Yin, J.; Guan, C.; Han, Y.; Gao, S.; Chen, Q. Appl. Phys. Lett. 2015, 106, 103109. doi:10.1063/1.4914968

Return to citation in text: [1] -

Sadewasser, S.; Glatzel, T., Eds. Kelvin Probe Force Microscopy: From Single Charge Detection to Device Characterization; Springer Series in Surface Sciences, Vol. 65; Springer, 2018. doi:10.1007/978-3-319-75687-5

Return to citation in text: [1] -

Melitz, W.; Shen, J.; Kummel, A. C.; Lee, S. Surf. Sci. Rep. 2011, 66, 1–27. doi:10.1016/j.surfrep.2010.10.001

Return to citation in text: [1] -

Binnig, G.; Quate, C. F.; Gerber, C. Phys. Rev. Lett. 1986, 56, 930–933. doi:10.1103/physrevlett.56.930

Return to citation in text: [1] -

Giessibl, F. J. Rev. Mod. Phys. 2003, 75, 949–983. doi:10.1103/revmodphys.75.949

Return to citation in text: [1] -

Albrecht, T. R.; Grütter, P.; Horne, D.; Rugar, D. J. Appl. Phys. 1991, 69, 668–673. doi:10.1063/1.347347

Return to citation in text: [1] -

Fernández Garrillo, P. A.; Grévin, B.; Chevalier, N.; Borowik, Ł. Rev. Sci. Instrum. 2018, 89, 043702. doi:10.1063/1.5007619

Return to citation in text: [1] -

Khoussa, H.; Baris, B.; Alchaar, M.; Chaumeton, F.; Ghamnia, M.; Gauthier, S.; Martrou, D. Phys. Status Solidi B 2018, 255, 1700482. doi:10.1002/pssb.201700482

Return to citation in text: [1] -

Ma, Z. M.; Kou, L.; Naitoh, Y.; Li, Y. J.; Sugawara, Y. Nanotechnology 2013, 24, 225701. doi:10.1088/0957-4484/24/22/225701

Return to citation in text: [1] -

Glatzel, T.; Sadewasser, S.; Shikler, R.; Rosenwaks, Y.; Lux-Steiner, M. C. Mater. Sci. Eng., B 2003, 102, 138–142. doi:10.1016/s0921-5107(03)00020-5

Return to citation in text: [1] -

Rosenwaks, Y.; Shikler, R.; Glatzel, T.; Sadewasser, S. Phys. Rev. B 2004, 70, 085320. doi:10.1103/physrevb.70.085320

Return to citation in text: [1] -

Wen, H. F.; Li, Y. J.; Arima, E.; Naitoh, Y.; Sugawara, Y.; Xu, R.; Cheng, Z. H. Nanotechnology 2017, 28, 105704. doi:10.1088/1361-6528/aa5aef

Return to citation in text: [1] -

Zou, S.; Yokoyama, H.; Sugawara, Y.; Li, Y. J. J. Phys. Chem. C 2020, 124, 21641–21645. doi:10.1021/acs.jpcc.0c07488

Return to citation in text: [1] -

Barth, C.; Henry, C. R. Nanotechnology 2006, 17, S155–S161. doi:10.1088/0957-4484/17/7/s09

Return to citation in text: [1] -

Barth, C.; Henry, C. R. J. Phys. Chem. C 2009, 113, 247–253. doi:10.1021/jp807340k

Return to citation in text: [1] -

Polak, L.; Wijngaarden, R. J. Phys. Rev. B 2016, 93, 195320. doi:10.1103/physrevb.93.195320

Return to citation in text: [1] -

Arita, M.; Torigoe, K.; Yamauchi, T.; Nagaoka, T.; Aiso, T.; Yamashita, Y.; Motooka, T. Appl. Phys. Lett. 2014, 104, 132103. doi:10.1063/1.4870419

Return to citation in text: [1] -

Sugawara, Y.; Miyazaki, M.; Li, Y. J. J. Phys. Commun. 2020, 4, 075015. doi:10.1088/2399-6528/aba477

Return to citation in text: [1] [2] -

Izumi, R.; Li, Y. J.; Naitoh, Y.; Sugawara, Y. Microscopy (Oxford, U. K.) 2022, 71, 98–103. doi:10.1093/jmicro/dfab055

Return to citation in text: [1] [2] [3] -

Dâna, A.; Yamamoto, Y. Nanotechnology 2005, 16, S125–S133. doi:10.1088/0957-4484/16/3/023

Return to citation in text: [1] [2] [3] [4] [5] [6] [7] -

Hudlet, S.; Saint Jean, M.; Roulet, B.; Berger, J.; Guthmann, C. J. Appl. Phys. 1995, 77, 3308–3314. doi:10.1063/1.358616

Return to citation in text: [1] [2] [3] [4] -

Sze, S. M.; Ng, K. K. Metal-Insulator-Semiconductor Capacitors. In Physics of semiconductor devices, 3rd ed.; Sze, S. M.; Ng, K. K., Eds.; John Wiley & Sons, 2006; pp 197–240. doi:10.1002/9780470068328.ch4

Return to citation in text: [1] [2] [3] [4] -

Selberherr, S. The Physical Parameters; Analysis and Simulation of Semiconductor Devices; Springer Vienna: Vienna, Austria, 1984; pp 80–126. doi:10.1007/978-3-7091-8752-4_4

Return to citation in text: [1] [2] [3] -

Schroder, D. K. Carrier Lifetimes. In Semiconductor material and device characterization; Schroder, D. K., Ed.; John Wiley & Sons, 2005; pp 389–464. doi:10.1002/0471749095.ch7

Return to citation in text: [1] [2] [3] [4] -

Sugimura, H.; Ishida, Y.; Hayashi, K.; Takai, O.; Nakagiri, N. Appl. Phys. Lett. 2002, 80, 1459–1461. doi:10.1063/1.1455145

Return to citation in text: [1] [2] -

Nakagiri, N.; Sugimura, H.; Ishida, Y.; Hayashi, K.; Takai, O. Surf. Sci. 2003, 532-535, 999–1003. doi:10.1016/s0039-6028(03)00456-4

Return to citation in text: [1] [2] -

Schumacher, Z.; Rejali, R.; Cowie, M.; Spielhofer, A.; Miyahara, Y.; Grutter, P. ACS Nano 2021, 15, 10377–10383. doi:10.1021/acsnano.1c02600

Return to citation in text: [1]

| 22. | Dâna, A.; Yamamoto, Y. Nanotechnology 2005, 16, S125–S133. doi:10.1088/0957-4484/16/3/023 |

| 22. | Dâna, A.; Yamamoto, Y. Nanotechnology 2005, 16, S125–S133. doi:10.1088/0957-4484/16/3/023 |

| 1. | Reed, M. L.; Plummer, J. D. J. Appl. Phys. 1988, 63, 5776–5793. doi:10.1063/1.340317 |

| 2. | Engel-Herbert, R.; Hwang, Y.; Stemmer, S. J. Appl. Phys. 2010, 108, 124101. doi:10.1063/1.3520431 |

| 3. | Guo, Y.; Wei, X.; Shu, J.; Liu, B.; Yin, J.; Guan, C.; Han, Y.; Gao, S.; Chen, Q. Appl. Phys. Lett. 2015, 106, 103109. doi:10.1063/1.4914968 |

| 11. | Ma, Z. M.; Kou, L.; Naitoh, Y.; Li, Y. J.; Sugawara, Y. Nanotechnology 2013, 24, 225701. doi:10.1088/0957-4484/24/22/225701 |

| 12. | Glatzel, T.; Sadewasser, S.; Shikler, R.; Rosenwaks, Y.; Lux-Steiner, M. C. Mater. Sci. Eng., B 2003, 102, 138–142. doi:10.1016/s0921-5107(03)00020-5 |

| 13. | Rosenwaks, Y.; Shikler, R.; Glatzel, T.; Sadewasser, S. Phys. Rev. B 2004, 70, 085320. doi:10.1103/physrevb.70.085320 |

| 14. | Wen, H. F.; Li, Y. J.; Arima, E.; Naitoh, Y.; Sugawara, Y.; Xu, R.; Cheng, Z. H. Nanotechnology 2017, 28, 105704. doi:10.1088/1361-6528/aa5aef |

| 23. | Hudlet, S.; Saint Jean, M.; Roulet, B.; Berger, J.; Guthmann, C. J. Appl. Phys. 1995, 77, 3308–3314. doi:10.1063/1.358616 |

| 24. | Sze, S. M.; Ng, K. K. Metal-Insulator-Semiconductor Capacitors. In Physics of semiconductor devices, 3rd ed.; Sze, S. M.; Ng, K. K., Eds.; John Wiley & Sons, 2006; pp 197–240. doi:10.1002/9780470068328.ch4 |

| 9. | Fernández Garrillo, P. A.; Grévin, B.; Chevalier, N.; Borowik, Ł. Rev. Sci. Instrum. 2018, 89, 043702. doi:10.1063/1.5007619 |

| 10. | Khoussa, H.; Baris, B.; Alchaar, M.; Chaumeton, F.; Ghamnia, M.; Gauthier, S.; Martrou, D. Phys. Status Solidi B 2018, 255, 1700482. doi:10.1002/pssb.201700482 |

| 25. | Selberherr, S. The Physical Parameters; Analysis and Simulation of Semiconductor Devices; Springer Vienna: Vienna, Austria, 1984; pp 80–126. doi:10.1007/978-3-7091-8752-4_4 |

| 26. | Schroder, D. K. Carrier Lifetimes. In Semiconductor material and device characterization; Schroder, D. K., Ed.; John Wiley & Sons, 2005; pp 389–464. doi:10.1002/0471749095.ch7 |

| 6. | Binnig, G.; Quate, C. F.; Gerber, C. Phys. Rev. Lett. 1986, 56, 930–933. doi:10.1103/physrevlett.56.930 |

| 7. | Giessibl, F. J. Rev. Mod. Phys. 2003, 75, 949–983. doi:10.1103/revmodphys.75.949 |

| 8. | Albrecht, T. R.; Grütter, P.; Horne, D.; Rugar, D. J. Appl. Phys. 1991, 69, 668–673. doi:10.1063/1.347347 |

| 23. | Hudlet, S.; Saint Jean, M.; Roulet, B.; Berger, J.; Guthmann, C. J. Appl. Phys. 1995, 77, 3308–3314. doi:10.1063/1.358616 |

| 4. | Sadewasser, S.; Glatzel, T., Eds. Kelvin Probe Force Microscopy: From Single Charge Detection to Device Characterization; Springer Series in Surface Sciences, Vol. 65; Springer, 2018. doi:10.1007/978-3-319-75687-5 |

| 5. | Melitz, W.; Shen, J.; Kummel, A. C.; Lee, S. Surf. Sci. Rep. 2011, 66, 1–27. doi:10.1016/j.surfrep.2010.10.001 |

| 23. | Hudlet, S.; Saint Jean, M.; Roulet, B.; Berger, J.; Guthmann, C. J. Appl. Phys. 1995, 77, 3308–3314. doi:10.1063/1.358616 |

| 24. | Sze, S. M.; Ng, K. K. Metal-Insulator-Semiconductor Capacitors. In Physics of semiconductor devices, 3rd ed.; Sze, S. M.; Ng, K. K., Eds.; John Wiley & Sons, 2006; pp 197–240. doi:10.1002/9780470068328.ch4 |

| 20. | Sugawara, Y.; Miyazaki, M.; Li, Y. J. J. Phys. Commun. 2020, 4, 075015. doi:10.1088/2399-6528/aba477 |

| 21. | Izumi, R.; Li, Y. J.; Naitoh, Y.; Sugawara, Y. Microscopy (Oxford, U. K.) 2022, 71, 98–103. doi:10.1093/jmicro/dfab055 |

| 22. | Dâna, A.; Yamamoto, Y. Nanotechnology 2005, 16, S125–S133. doi:10.1088/0957-4484/16/3/023 |

| 19. | Arita, M.; Torigoe, K.; Yamauchi, T.; Nagaoka, T.; Aiso, T.; Yamashita, Y.; Motooka, T. Appl. Phys. Lett. 2014, 104, 132103. doi:10.1063/1.4870419 |

| 23. | Hudlet, S.; Saint Jean, M.; Roulet, B.; Berger, J.; Guthmann, C. J. Appl. Phys. 1995, 77, 3308–3314. doi:10.1063/1.358616 |

| 18. | Polak, L.; Wijngaarden, R. J. Phys. Rev. B 2016, 93, 195320. doi:10.1103/physrevb.93.195320 |

| 15. | Zou, S.; Yokoyama, H.; Sugawara, Y.; Li, Y. J. J. Phys. Chem. C 2020, 124, 21641–21645. doi:10.1021/acs.jpcc.0c07488 |

| 16. | Barth, C.; Henry, C. R. Nanotechnology 2006, 17, S155–S161. doi:10.1088/0957-4484/17/7/s09 |

| 17. | Barth, C.; Henry, C. R. J. Phys. Chem. C 2009, 113, 247–253. doi:10.1021/jp807340k |

| 22. | Dâna, A.; Yamamoto, Y. Nanotechnology 2005, 16, S125–S133. doi:10.1088/0957-4484/16/3/023 |

| 26. | Schroder, D. K. Carrier Lifetimes. In Semiconductor material and device characterization; Schroder, D. K., Ed.; John Wiley & Sons, 2005; pp 389–464. doi:10.1002/0471749095.ch7 |

| 25. | Selberherr, S. The Physical Parameters; Analysis and Simulation of Semiconductor Devices; Springer Vienna: Vienna, Austria, 1984; pp 80–126. doi:10.1007/978-3-7091-8752-4_4 |

| 26. | Schroder, D. K. Carrier Lifetimes. In Semiconductor material and device characterization; Schroder, D. K., Ed.; John Wiley & Sons, 2005; pp 389–464. doi:10.1002/0471749095.ch7 |

| 25. | Selberherr, S. The Physical Parameters; Analysis and Simulation of Semiconductor Devices; Springer Vienna: Vienna, Austria, 1984; pp 80–126. doi:10.1007/978-3-7091-8752-4_4 |

| 26. | Schroder, D. K. Carrier Lifetimes. In Semiconductor material and device characterization; Schroder, D. K., Ed.; John Wiley & Sons, 2005; pp 389–464. doi:10.1002/0471749095.ch7 |

| 22. | Dâna, A.; Yamamoto, Y. Nanotechnology 2005, 16, S125–S133. doi:10.1088/0957-4484/16/3/023 |

| 27. | Sugimura, H.; Ishida, Y.; Hayashi, K.; Takai, O.; Nakagiri, N. Appl. Phys. Lett. 2002, 80, 1459–1461. doi:10.1063/1.1455145 |

| 28. | Nakagiri, N.; Sugimura, H.; Ishida, Y.; Hayashi, K.; Takai, O. Surf. Sci. 2003, 532-535, 999–1003. doi:10.1016/s0039-6028(03)00456-4 |

| 29. | Schumacher, Z.; Rejali, R.; Cowie, M.; Spielhofer, A.; Miyahara, Y.; Grutter, P. ACS Nano 2021, 15, 10377–10383. doi:10.1021/acsnano.1c02600 |

| 20. | Sugawara, Y.; Miyazaki, M.; Li, Y. J. J. Phys. Commun. 2020, 4, 075015. doi:10.1088/2399-6528/aba477 |

| 22. | Dâna, A.; Yamamoto, Y. Nanotechnology 2005, 16, S125–S133. doi:10.1088/0957-4484/16/3/023 |

| 27. | Sugimura, H.; Ishida, Y.; Hayashi, K.; Takai, O.; Nakagiri, N. Appl. Phys. Lett. 2002, 80, 1459–1461. doi:10.1063/1.1455145 |

| 28. | Nakagiri, N.; Sugimura, H.; Ishida, Y.; Hayashi, K.; Takai, O. Surf. Sci. 2003, 532-535, 999–1003. doi:10.1016/s0039-6028(03)00456-4 |

| 21. | Izumi, R.; Li, Y. J.; Naitoh, Y.; Sugawara, Y. Microscopy (Oxford, U. K.) 2022, 71, 98–103. doi:10.1093/jmicro/dfab055 |

| 22. | Dâna, A.; Yamamoto, Y. Nanotechnology 2005, 16, S125–S133. doi:10.1088/0957-4484/16/3/023 |

| 24. | Sze, S. M.; Ng, K. K. Metal-Insulator-Semiconductor Capacitors. In Physics of semiconductor devices, 3rd ed.; Sze, S. M.; Ng, K. K., Eds.; John Wiley & Sons, 2006; pp 197–240. doi:10.1002/9780470068328.ch4 |

| 24. | Sze, S. M.; Ng, K. K. Metal-Insulator-Semiconductor Capacitors. In Physics of semiconductor devices, 3rd ed.; Sze, S. M.; Ng, K. K., Eds.; John Wiley & Sons, 2006; pp 197–240. doi:10.1002/9780470068328.ch4 |

| 21. | Izumi, R.; Li, Y. J.; Naitoh, Y.; Sugawara, Y. Microscopy (Oxford, U. K.) 2022, 71, 98–103. doi:10.1093/jmicro/dfab055 |

© 2023 Izumi et al.; licensee Beilstein-Institut.

This is an open access article licensed under the terms of the Beilstein-Institut Open Access License Agreement (https://www.beilstein-journals.org/bjnano/terms), which is identical to the Creative Commons Attribution 4.0 International License (https://creativecommons.org/licenses/by/4.0). The reuse of material under this license requires that the author(s), source and license are credited. Third-party material in this article could be subject to other licenses (typically indicated in the credit line), and in this case, users are required to obtain permission from the license holder to reuse the material.