Abstract

In this paper, a new nanoscale double-gate junctionless tunneling field-effect transistor (DG-JL TFET) based on a Si1−xGex/Si/Ge heterojunction (HJ) structure is proposed to achieve an improved electrical performance. The effect of introducing the Si1−xGex material at the source side on improving the subthreshold behavior of the DG-JL TFET and on suppressing ambipolar conduction is investigated. Moreover, the impact of the Ge mole fraction in the proposed Si1−xGex source region on the electrical figures of merit (FoMs) of the transistor, including the swing factor and the ION/IOFF ratio is analyzed. It is found that the optimized design with 60 atom % of Ge offers improved switching behavior and enhanced derived current capability at the nanoscale level, with a swing factor of 42 mV/dec and an ION/IOFF ratio of 115 dB. Further, the scaling capability of the proposed Si1−xGex/Si/Ge DG-HJ-JL TFET structure is investigated and compared to that of a conventional Ge-DG-JL TFET design, where the optimized design exhibits an improved switching behavior at the nanoscale level. These results make the optimized device suitable for designing digital circuit for high-performance nanoelectronic applications.

Introduction

In the last years, the continuous miniaturization of nanoscale transistors induces new challenges including short-channel effects (SCEs) and high power consumption, which prevent incorporating conventional metal-oxide semiconductor field-effect transistors (MOSFETs) and their complements in nanoelectronic circuit designs [1-4]. In this context, small swing-switch devices such as double-gate tunneling field-effect transistors (DG TFETs) are gaining attention because of their good subthreshold characteristics, high scalability and low OFF-current [5-8]. The main idea behind this innovative device is the use of a gated p-i-n diode, the working mechanism of which is based on a quantum band-to-band tunneling effect. This makes it more immune against the undesired SCEs and enables a better scaling capability. Despite such attractive properties, DG TFETs still suffer from other issues mainly related to the relatively low ON-state current and the severe ambipolar conduction, which make it extremely challenging for designing high-performance digital nanocircuits [7-9]. Consequently, intensive efforts have been paid to address these limitations by proposing new designs based on heterostructures, gate engineering and high-k dielectrics [9-12]. Nanoscale DG TFETs are believed to face an upward amendment to meet the difficulty of decreasing the huge thermal budget required for the formation of the gated p-i-n diode structure. Moreover, in spite of the actual mature experimental techniques, realizing metallurgical junctions in sub-32 nm nodes is considered extremely difficult [13-15]. For this purpose, the junctionless (JL) design is considered the best approach to avoid the above outlined experimental limitations and achieve significant improvements regarding the transistor manufacturing cost [14-17]. The JL technology is considered to be cost-effective and allows avoiding the high thermal budget [15-17]. The concept of a gated source is used for the JL technology in order to ensure the band-to-band tunneling effect, while materials with high work function are required to generate the tunnel current. In other words, the channel is assumed to be a uniformly and highly doped n-type material, and in order to ensure the band-to-band tunneling effect, the source is supported with a control gate to make the device behave like a conventional p-i-n-based TFET [18]. However, the most pronounced drawbacks associated with the DG TFETs design also persist in the JL structure, namely the low ON-state current, the high leakage current and parasitic ambipolar conduction, which can eventually prevent the application in high-performance nanoelectronic circuits. The DG-JL TFET design can pave the way to reduce the fabrication cost, but it exhibits degraded electrical FoMs. Several recently published works are focused on improving the multi-gate JL TFET by suggesting design improvements such as gate underlap and overlap, introducing III–V materials and source/drain engineering [19-24]. Additional approaches are in fact required in order to push the limits of the DG-JL TFET performance and achieve energy-efficient and scalable transistors. To the best of our knowledge, no design approach based on Si1−xGex/Si/Ge heterochannels with optimized Ge content was proposed to improve the electrical performance and to suppress the parasitic ambipolar conduction in DG-JL TFETs. We present in this paper, a new DG-HJ-JL TFET design to achieve improved electrical FoMs and reduced fabrication cost. An exhaustive numerical study of the electrical behavior of the proposed device at the nanoscale level is performed using the ATLAS 2-D simulation software [25]. Further, the impact of the Ge content on the electrical performance of the transistor is investigated. It is found that the proposed design offers between improved derived current capability and reduced ambipolar conduction compared to a conventional DG Ge-JL-TFET design. In order to consolidate our investigation, the scaling capability of the proposed design is investigated and compared to that of the conventional counterpart, where the proposed structure demonstrates a superior switching behavior. This makes the optimized structure a potential alternative for providing energy-efficient transistors with suppressed ambipolar conduction for designing high-performance nanoelectronic circuits at low manufacturing cost.

Numerical Simulations

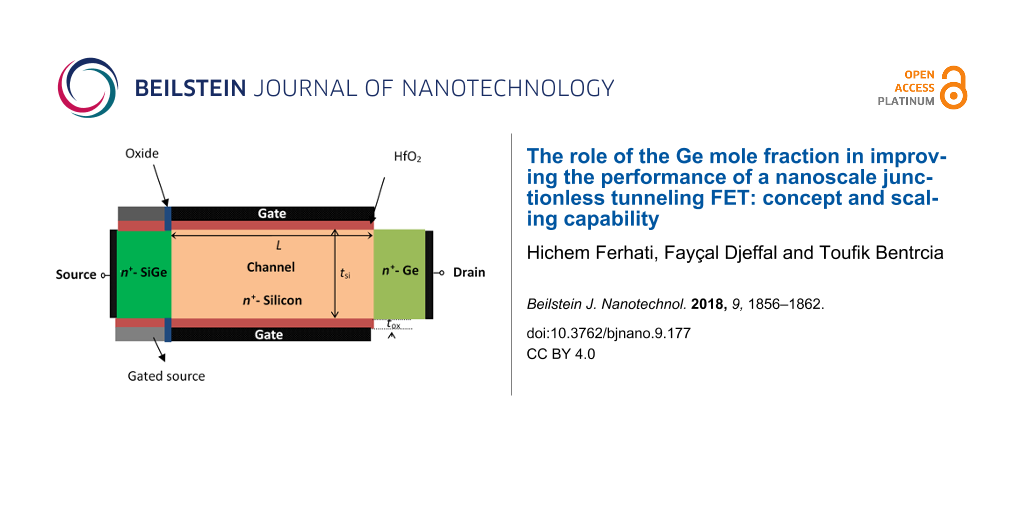

Figure 1 describes schematically the investigated DG-HJ-JL TFET structure. The cornerstone of the proposed design is the assumption of a uniformly and highly doped heterochannel (Si1−xGex/Si/Ge), which can be indicated by n+/n+/n+. In addition, the proposed design is suggested with a HfO2 gate dielectric in order to ensure a good electrostatic control of the channel, with tox representing its thickness. Moreover, the material of the gated source is assumed to have a high work function value of 5.6 eV in order to guarantee the tunnel effect, while the work function of the channel gate is set equal to 4.3 eV. In Figure 1, L is the channel length, tch refers to the channel thickness, Nd is the doping concentration of the channel, and Ls and Ld denote the extension lengths of source and drain, respectively.

![[2190-4286-9-177-1]](/bjnano/content/figures/2190-4286-9-177-1.png?scale=2.0&max-width=1024&background=FFFFFF)

Figure 1: Schematic of the investigated DG-HJ-JL TFET with Nd = 1·1019 cm−3 and tox = 3 nm.

Figure 1: Schematic of the investigated DG-HJ-JL TFET with Nd = 1·1019 cm−3 and tox = 3 nm.

The accurate modeling of the nanoscale DG-HJ-JL TFET requires taking into account quantum-confinement effects, which lead to some modeling bottlenecks associated with the models of the carrier density gradient. Furthermore, since the investigated transistor is considered as a quantum mechanical device, complicated systems of equations resulted from the necessity of considering the band-to-band quantum tunneling effects. These nonlinear equations impose many mathematical difficulties, which complicate the analytical modeling of the nanoscale device performance. Numerical approaches are used to deal with the above outlined problems. The ATLAS 2D device simulator using the S-PISCES module has emerged recently as a useful and realistic tool for numerically modeling the electrostatic behavior of transistors [25].

The electrostatic behavior of the investigated nanoscale (Si1-xGex/Si/Ge) DG-HJ-JL TFET including the tunnel effects is modeled using the nonlocal-BTBT command, which takes into account nonlocal band-to-band quantum tunneling [25]. In this perspective, the tunnel current is generated near the source/channel junction and can be characterized by a transfer of electrons and holes across this junction. Hence, the tunneling current for an electron with longitudinal energy E and transverse energy ET can be expressed as follows [25]:

where T(E) represents the tunneling probability of the electrons, q is the electron charge, me and mh are the effective masses of electrons and holes, respectively, h is the Planck constant. fl and fr are the Fermi–Dirac distributions on the left and the right side of the source/channel junction, respectively:

where, EfSiGe and EfSi are the Fermi levels at the Si1−xGex source and Si channel regions, respectively, kB is the Boltzmann constant and T the temperature.

In order to reflect accurately the device behavior for very short dimensions like in our case, the modified drift–diffusion model, which includes other effects related to the short-channel nature of the investigated transistor and to quantum effects is used. Further, the gradient density model is also included, which consists of the quantum correction associated with the local potential to the carrier temperatures in the current equations [25]. Moreover, models for carrier recombination (Shockley–Read–Hall (SRH), Auger and surface recombination) are also adopted [26]. In fact, the carrier mobility mainly depends on three quantities, transverse and parallel electric field, doping and temperature, which were combined using Matthiessen’s formula. Accordingly, the Lombardi model (CVT) is used to express the carrier mobility in the channel [27]. Moreover, the intrinsic parameters of the materials (Si, Si1−xGex and Ge) such as band gap, mobility and the density of states were considered to be dependent on the Ge mole fraction (xGe). It should be noted that the Ge mole fraction is varied from 0 to 0.7. This corresponds to the experimental limit for growing Si1−xGex when avoiding interfacial defects at the considered device thickness tch = 5 nm [28].

Results and Discussion

The main idea behind the proposed design is a modified heterostructured channel. In this context, it seems important to analyze the electrical behavior of the proposed design with considering different material configurations at the source, drain and channel regions in order to distinguish which heterochannel design provides the best electrical performance. Figure 2 depicts Ids–Vgs characteristics of the proposed design with different material configurations of the heterochannel compared to that of the conventional designs with Lg = 20 nm, Ls = 10 nm and Nd = 1·1019 cm−3.

![[2190-4286-9-177-2]](/bjnano/content/figures/2190-4286-9-177-2.png?scale=2.0&max-width=1024&background=FFFFFF)

Figure 2: Drain current as a function of the applied gate voltage for the DG-HJ-JL TFET proposed with different heterochannel configurations compared to that of the conventional homochannel designs (Lg = 20 nm, Ls = 10 nm and Nd = 1·1019 cm−3, tch = 5 nm and Vds = 1 V).

Figure 2: Drain current as a function of the applied gate voltage for the DG-HJ-JL TFET proposed with differe...

The proposed DG-HJ-JL TFET design with Ge/Si/Ge channel structure exhibits better electrostatic behavior and less parasitic ambipolar conduction than the other designs. In fact, this behavior can be attributed to two essential effects: Firstly, the enhanced tunneling current resulting from the low tunneling barrier giving rise to a higher probability of electron transfer at the source/channel interface. Secondly, the heterostructure at the channel/drain interface can be beneficial for sufficiently enlarging the tunneling barrier under reverse-bias conditions in order to effectively suppress the undesired ambipolar conduction. Moreover, we can notice that the conventional design with Si channel shows a reduced OFF-state current compared to that of the investigated heterochannel designs, which is mainly due to the high band-gap energy and the low electron mobility associated to Si. On the other hand, the conventional Ge-DG-JL TFET design provides higher ON-state current. This is due to the smaller band gap energy of Ge, yielding a higher tunneling efficiency. Moreover, the higher electron mobility of Ge (3900 cm2·V−1·s−1) contributes to the increased drain current at the threshold voltage as compared to the conventional design with silicon (1400 cm2·V−1·s−1) channel. A suitable choice of the channel material can offer the possibility of enhancing the ION/IOFF ratio as well as achieving a lower swing factor. For this purpose, introducing Si1−xGex material at the source side can be useful for achieving an improved electrical behavior through modulating the tunneling barrier width at the source/channel junction by varying the Ge concentration.

Figure 3a shows the transfer characteristics associated of the proposed Si1−xGex/Si/Ge DG-HJ-JL TFET design with different Ge mole fractions. Increasing the Ge content leads to an increase of the drain current. This is mainly due to the enhanced carrier mobility caused by the increased Ge content. Moreover, introducing SiGe at the source side can be effective for reducing the tunneling barrier. Besides, the Ge concentration increase induces a lowering of the tunneling barrier, which enables enhancing the derived current capability as shown in Figure 3a. It can be also concluded that the Ge mole fraction modulates the threshold voltage for the tunnel-current generation, which can in turn influence greatly the subthreshold behavior of the device. Moreover, the proposed Si1−xGex/Si/Ge heterochannel enables a superior control of the channel conductivity through modulating the electric field at the heterojunction interfaces. In this regard, it is of great importance to illustrate the electric field distribution for a better understanding of the physical rules governing the obtained improvements of the electrostatic behavior. Figure 3b compares the distribution of the electric field along the channel of the proposed Si1−xGex/Si/Ge DG-HJ-JL TFET design to that of the conventional Ge-DG-JL TFET counterpart. Clearly, a considerable change in the electric field distribution can be achieved by including the heterochannel, with higher electric field arising in the source/channel interface as well as along the channel. This indicates that by a proper choice of the channel material, we can achieve an enhanced electrostatic behavior. This enables improving the carrier transport efficiency and thereby the device derived current capability at the nanoscale level.

![[2190-4286-9-177-3]](/bjnano/content/figures/2190-4286-9-177-3.png?scale=2.0&max-width=1024&background=FFFFFF)

Figure 3: (a) Transfer characteristics of the proposed Si1−xGex/Si/Ge DG-HJ-JL TFET as a function of the Ge concentration with Nd = 1·1019 cm−3, Vds = 1 V, tox = 2 nm, Lg = 20 nm and tch = 5 nm. (b) Distribution of the electric field along the channel of the proposed Si1−xGex/Si/Ge DG-HJ-JL TFET structure and the conventional Ge-DG-JL TFET design with Nd = 1·1019 cm−3, tch = 5 nm, tox = 2 nm, Lg = 20 nm and Ls = 10 nm.

Figure 3: (a) Transfer characteristics of the proposed Si1−xGex/Si/Ge DG-HJ-JL TFET as a function of the Ge c...

In order to get a qualitative idea about the impact of the Ge concentration on the electrical performance of the proposed DG-HJ-JL TFET design, Figure 4a shows both ION/IOFF ratio and the subthreshold swing factor as functions of the Ge mole fraction. By increasing the Ge content, the ION/IOFF ratio increases significantly to reach its maximum for a Ge mole fraction value of 0.6 and saturates after this value. Moreover, the ION/IOFF ratio of the proposed DG-HJ-JL TFET is higher than that of the conventional structure with uniform channel. This can be attributed to the enhanced tunneling current resulting from the change of the tunneling barrier with increasing Ge content. Figure 4b compares the band diagrams of the DG-HJ-JL TFET design and the conventional structure with uniform Si channel. Figure 4b reveals that by introducing Si1−xGex, the tunneling barrier height at the source–channel junction decreases and a higher tunneling current can be generated when the band alignment at the junction is satisfied.

In addition, Figure 4 shows the complex subthreshold behavior. The Ge mole fraction induces a highly non-linear behavior of the swing factor as it is shown in Figure 4a. This phenomenon can be ascribed to the quantum nature of the band-to-band tunneling effects, and determining the Ge concentration that provides an enhanced subthreshold behavior seems to be very complex at the nanoscale level. The swing factor decreases significantly above xGe = 0.3, which can be explained by the effect of the tunneling barrier height on the device subthreshold behavior. At a Ge mole fraction of 0.6, a good trade-off between derived current capability and subthreshold behavior is obtained, with an ION/IOFF ratio value of 115 dB and a swing factor value of 42 mV/dec at the nanoscale level (Lg = 20nm) as it is illustrated in Figure 4a.

![[2190-4286-9-177-4]](/bjnano/content/figures/2190-4286-9-177-4.png?scale=2.0&max-width=1024&background=FFFFFF)

Figure 4: (a) Subthreshold swing factor and the ION/IOFF ratio as functions of the Ge mole fraction for the investigated Si1−xGex/Si/Ge DG-HJ-JL TFET structure with Nd = 1·1019 cm−3, Vds = 1 V, tox = 2 nm, Lg = 20 nm and tch = 5 nm. (b) Comparison of the band diagrams of the proposed Si1−xGex/Si/Ge DG-HJ-JL TFET design and the conventional structure with uniform Si channel.

Figure 4: (a) Subthreshold swing factor and the ION/IOFF ratio as functions of the Ge mole fraction for the i...

More importantly, we analyze the impact of the optimized Si1−xGex/Si/Ge heterochannel structure on the device scaling capability for high-performance nanoelectronic applications. Figure 5 depicts the swing factor as a function of the transistor channel length for both the proposed Si1−xGex/Si/Ge DG-HJ-JL TFET design and the conventional Ge-DG-JL TFET structure with tch = 5 nm, xGe = 0.6 and Nd = 1·1019 cm−3. The optimized design provides better scaling capability than the conventional one and exhibits a faster decrease of the swing factor as a function of the channel length. This behavior can be explained by the improved electrostatic response offered by the heterochannel.

![[2190-4286-9-177-5]](/bjnano/content/figures/2190-4286-9-177-5.png?scale=2.0&max-width=1024&background=FFFFFF)

Figure 5: Subthreshold swing factor as a function of the channel length for both the proposed Si1−xGex/Si/Ge DG-HJ-JL TFET and the conventional Ge-DG-JL TFET with Nd = 1·1019 cm−3, Vds = 1 V, tox = 2 nm, Ls = 10 nm and tch = 5nm.

Figure 5: Subthreshold swing factor as a function of the channel length for both the proposed Si1−xGex/Si/Ge ...

For the completeness of this work, we analyze the improvements of the proposed design compared to conventional TFET devices with regard to the electrical performance. Table 1 summarizes an overall comparison of electrical metrics between the proposed Si1−xGex/Si/Ge DG-HJ-JL TFET, the conventional Ge-DG-JL TFET design and the numerical results associated to the conventional Si-DG-JL TFET [18]. it reveals that the proposed design with heterochannel outperforms considerably the conventional counterparts, with 58% improvement regarding the subthreshold swing factor and 54% enhancement in terms of the ION/IOFF ratio. The optimized design improves the device tunneling performance, not only through a more effective carrier-transport mechanism, but also through a distinctive reduction of the undesired ambipolar conduction.

Table 1: Overall electrical comparison of FoMs.

| conventional Ge-DG-JL TFET design | proposed Si1−xGex/Si/Ge DG-HJ-JL TFET structure | conventional Si-JL TFET structure [18] | |

|---|---|---|---|

| design variables | |||

| channel length Lg (nm) | 20 | 20 | 20 |

| source/drain extensions length Ls/d (nm) | 10 | 10 | 25 |

| dielectric permittivity | 25 | 25 | 25 |

| oxide thickness tox (nm) | 2 | 2 | 2 |

| channel thickness tch (nm) | 5 | 5 | 5 |

| gate work function (eV) | 4.3 | 4.3 | 4.3 |

| gated source work function (eV) | 5.6 | 5.6 | 5.9 |

| channel doping concentration Nd (cm−3) | 1·1019, n-type | 1·1019, n-type | 1·1019, n-type |

| drain voltage Vds (V) | 1 | 1 | 1 |

| Ge mole fraction of Si1−xGex source | — | 60 | — |

| performance parameters | |||

| subthreshold swing (mV/dec) | 114 | 42 | 81 |

| ION/IOFF ratio (dB) | 79 | 115 | 98 |

| ambipolar conduction | high | suppressed | high |

Conclusion

In this work, a new DG-JL TFET design with a heterochannel (Si1−xGex/Si/Ge) has been proposed as a new way to achieve enhanced electrical performance and suppressed ambipolar conduction. It has been concluded from the obtained results that the investigated DG-HJ-JL TFET design offers the possibility to overcome the trade-off between improved switching characteristic and superior derived current capability. In addition, the impact of the Ge concentration on the electrical behavior of the device has been analyzed. It has been deduced that the proposed design with 60% of Ge provides an ION/IOFF ratio of 115 dB and a swing factor of 42 mV/dec. It has been also concluded that the optimized design offers superior scaling capability compared to the conventional Ge-DG-JL TFET structure. Therefore, the optimized design opens up the route for achieving an enhanced derived current capability with suppressed ambipolar conduction and for improving the device subthreshold behavior at the nanoscale level. This makes the optimized Si1−xGex/Si/Ge DG-HJ-JL TFET design a potential alternative for high-performance nanoelectronic applications. Moreover, this study can be extended by investigating the impact of other parameters such as the interfacial defects between both Si and SiGe materials and the degradation-related ageing effects including stress. To do so, new complex models and numerical simulations need to be developed.

References

-

International Technology Roadmap for Semiconductors - ITRS 2.0 Home Page. http://itrs2.net (accessed June 8, 2018).

Return to citation in text: [1] -

Chen, Q.; Meindl, J. D. Nanotechnology 2004, 15, S549. doi:10.1088/0957-4484/15/10/009

Return to citation in text: [1] -

Frank, D. J.; Dennard, R. H.; Nowak, E.; Solomon, P. M.; Taur, Y.; Wong, H.-S. P. Proc. IEEE 2001, 89, 259–288. doi:10.1109/5.915374

Return to citation in text: [1] -

Mamaluy, D.; Gao, X. Appl. Phys. Lett. 2015, 106, 193503. doi:10.1063/1.4919871

Return to citation in text: [1] -

Ionescu, A. M.; Riel, H. Nature 2011, 479, 329–337. doi:10.1038/nature10679

Return to citation in text: [1] -

Seabaugh, A. C.; Zhang, Q. Proc. IEEE 2010, 98, 2095–2110. doi:10.1109/JPROC.2010.2070470

Return to citation in text: [1] -

Choi, W. Y.; Park, B.-G.; Lee, J. D.; Liu, T.-J. K. IEEE Electron Device Lett. 2007, 28, 743–745. doi:10.1109/LED.2007.901273

Return to citation in text: [1] [2] -

Avci, U. E.; Morris, D. H.; Young, I. A. IEEE J. Electron Devices Soc. 2015, 3, 88–95. doi:10.1109/JEDS.2015.2390591

Return to citation in text: [1] [2] -

Esseni, D.; Guglielmini, M.; Kapidani, B.; Rollo, T.; Alioto, M. IEEE Trans. VLSI Syst. 2014, 22, 2488–2498. doi:10.1109/TVLSI.2013.2293135

Return to citation in text: [1] [2] -

Seema; Chauhan, S. S. Superlattices Microstruct. 2018, 117, 1–8. doi:10.1016/j.spmi.2018.03.002

Return to citation in text: [1] -

Abdi, D. B.; Kumar, M. J. IEEE J. Electron Devices Soc. 2014, 2, 187–190. doi:10.1109/JEDS.2014.2327626

Return to citation in text: [1] -

Gundapaneni, S.; Bajaj, M.; Pandey, R. K.; Murali, K. V. R. M.; Ganguly, S.; Kottantharayil, A. IEEE Trans. Electron Devices 2012, 59, 1023–1029. doi:10.1109/TED.2012.2185800

Return to citation in text: [1] -

Boucart, K.; Ionescu, A. M. IEEE Trans. Electron Devices 2007, 54, 1725–1733. doi:10.1109/TED.2007.899389

Return to citation in text: [1] -

Chebaki, E.; Djeffal, F.; Ferhati, H.; Bentrcia, T. Superlattices Microstruct. 2016, 92, 80–91. doi:10.1016/j.spmi.2016.02.009

Return to citation in text: [1] [2] -

Djeffal, F.; Ferhati, H.; Bentrcia, T. Superlattices Microstruct. 2016, 90, 132–140. doi:10.1016/j.spmi.2015.09.041

Return to citation in text: [1] [2] [3] -

Lee, C.-W.; Afzalian, A.; Akhavan, N. D.; Yan, R.; Ferain, I.; Colinge, J.-P. Appl. Phys. Lett. 2009, 94, 053511. doi:10.1063/1.3079411

Return to citation in text: [1] [2] -

Colinge, J.-P.; Lee, C.-W.; Afzalian, A.; Akhavan, N. D.; Yan, R.; Ferain, I.; Razavi, P.; Neill, B. N. O.; Blake, A.; White, M.; Kelleher, A.-M.; Carthy, B.; Murphy, R. Nat. Nanotechnol. 2010, 5, 225–229. doi:10.1038/nnano.2010.15

Return to citation in text: [1] [2] -

Ghosh, B.; Akram, M. W. IEEE Electron Device Lett. 2013, 34, 584–586. doi:10.1109/LED.2013.2253752

Return to citation in text: [1] [2] [3] -

Yadav, D. S.; Sharma, D.; Raad, B. R.; Bajaj, V. Superlattices Microstruct. 2016, 96, 36–46. doi:10.1016/j.spmi.2016.04.027

Return to citation in text: [1] -

Goswami, Y.; Ghosh, B.; Asthana, P. K. RSC Adv. 2014, 4, 10761–10765. doi:10.1039/C3RA46535G

Return to citation in text: [1] -

Imen Abadi, R. M.; Sedigh Ziabari, S. A. Appl. Phys. A 2016, 122, 988. doi:10.1007/s00339-016-0530-9

Return to citation in text: [1] -

Raad, B. R.; Sharma, D.; Kondekar, P.; Nigam, K.; Yadav, D. S. IEEE Trans. Electron Devices 2016, 63, 3950–3957. doi:10.1109/TED.2016.2600621

Return to citation in text: [1] -

Yu, T.-Y.; Peng, L.-S.; Lin, C.-W.; Hsin, Y.-M. Microelectron. Reliab. 2018, 83, 235–237. doi:10.1016/j.microrel.2017.05.017

Return to citation in text: [1] -

Raad, B. R.; Sharma, D.; Tirkey, S. Microelectron. Eng. 2018, 194, 79–84. doi:10.1016/j.mee.2018.03.007

Return to citation in text: [1] -

ATLAS User's manual device simulation software; Silvaco Int. Ltd.: Santa Clara, CA, U.S.A., 2012.

Return to citation in text: [1] [2] [3] [4] [5] -

Lombardi, C.; Manzini, S.; Saporito, A.; Vanzi, M. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 1988, 7, 1164–1171. doi:10.1109/43.9186

Return to citation in text: [1] -

Shockley, W.; Read, W. T., Jr. Phys. Rev. 1952, 87, 835. doi:10.1103/PhysRev.87.835

Return to citation in text: [1] -

Konig, U. N- and p-type Si-SiGe hetero FETs. In High Performance Electron Devices for Microwave and Optoelectronic Applications, 2000 8th IEEE International Symposium on, Glasgow, United Kingdom, Nov 14, 2000; IEEE Publishing: Piscataway, NJ, U.S.A.. doi:10.1109/EDMO.2000.919017

Return to citation in text: [1]

| 18. | Ghosh, B.; Akram, M. W. IEEE Electron Device Lett. 2013, 34, 584–586. doi:10.1109/LED.2013.2253752 |

| 28. | Konig, U. N- and p-type Si-SiGe hetero FETs. In High Performance Electron Devices for Microwave and Optoelectronic Applications, 2000 8th IEEE International Symposium on, Glasgow, United Kingdom, Nov 14, 2000; IEEE Publishing: Piscataway, NJ, U.S.A.. doi:10.1109/EDMO.2000.919017 |

| 18. | Ghosh, B.; Akram, M. W. IEEE Electron Device Lett. 2013, 34, 584–586. doi:10.1109/LED.2013.2253752 |

| 1. | International Technology Roadmap for Semiconductors - ITRS 2.0 Home Page. http://itrs2.net (accessed June 8, 2018). |

| 2. | Chen, Q.; Meindl, J. D. Nanotechnology 2004, 15, S549. doi:10.1088/0957-4484/15/10/009 |

| 3. | Frank, D. J.; Dennard, R. H.; Nowak, E.; Solomon, P. M.; Taur, Y.; Wong, H.-S. P. Proc. IEEE 2001, 89, 259–288. doi:10.1109/5.915374 |

| 4. | Mamaluy, D.; Gao, X. Appl. Phys. Lett. 2015, 106, 193503. doi:10.1063/1.4919871 |

| 13. | Boucart, K.; Ionescu, A. M. IEEE Trans. Electron Devices 2007, 54, 1725–1733. doi:10.1109/TED.2007.899389 |

| 14. | Chebaki, E.; Djeffal, F.; Ferhati, H.; Bentrcia, T. Superlattices Microstruct. 2016, 92, 80–91. doi:10.1016/j.spmi.2016.02.009 |

| 15. | Djeffal, F.; Ferhati, H.; Bentrcia, T. Superlattices Microstruct. 2016, 90, 132–140. doi:10.1016/j.spmi.2015.09.041 |

| 26. | Lombardi, C.; Manzini, S.; Saporito, A.; Vanzi, M. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 1988, 7, 1164–1171. doi:10.1109/43.9186 |

| 9. | Esseni, D.; Guglielmini, M.; Kapidani, B.; Rollo, T.; Alioto, M. IEEE Trans. VLSI Syst. 2014, 22, 2488–2498. doi:10.1109/TVLSI.2013.2293135 |

| 10. | Seema; Chauhan, S. S. Superlattices Microstruct. 2018, 117, 1–8. doi:10.1016/j.spmi.2018.03.002 |

| 11. | Abdi, D. B.; Kumar, M. J. IEEE J. Electron Devices Soc. 2014, 2, 187–190. doi:10.1109/JEDS.2014.2327626 |

| 12. | Gundapaneni, S.; Bajaj, M.; Pandey, R. K.; Murali, K. V. R. M.; Ganguly, S.; Kottantharayil, A. IEEE Trans. Electron Devices 2012, 59, 1023–1029. doi:10.1109/TED.2012.2185800 |

| 27. | Shockley, W.; Read, W. T., Jr. Phys. Rev. 1952, 87, 835. doi:10.1103/PhysRev.87.835 |

| 7. | Choi, W. Y.; Park, B.-G.; Lee, J. D.; Liu, T.-J. K. IEEE Electron Device Lett. 2007, 28, 743–745. doi:10.1109/LED.2007.901273 |

| 8. | Avci, U. E.; Morris, D. H.; Young, I. A. IEEE J. Electron Devices Soc. 2015, 3, 88–95. doi:10.1109/JEDS.2015.2390591 |

| 9. | Esseni, D.; Guglielmini, M.; Kapidani, B.; Rollo, T.; Alioto, M. IEEE Trans. VLSI Syst. 2014, 22, 2488–2498. doi:10.1109/TVLSI.2013.2293135 |

| 25. | ATLAS User's manual device simulation software; Silvaco Int. Ltd.: Santa Clara, CA, U.S.A., 2012. |

| 5. | Ionescu, A. M.; Riel, H. Nature 2011, 479, 329–337. doi:10.1038/nature10679 |

| 6. | Seabaugh, A. C.; Zhang, Q. Proc. IEEE 2010, 98, 2095–2110. doi:10.1109/JPROC.2010.2070470 |

| 7. | Choi, W. Y.; Park, B.-G.; Lee, J. D.; Liu, T.-J. K. IEEE Electron Device Lett. 2007, 28, 743–745. doi:10.1109/LED.2007.901273 |

| 8. | Avci, U. E.; Morris, D. H.; Young, I. A. IEEE J. Electron Devices Soc. 2015, 3, 88–95. doi:10.1109/JEDS.2015.2390591 |

| 25. | ATLAS User's manual device simulation software; Silvaco Int. Ltd.: Santa Clara, CA, U.S.A., 2012. |

| 19. | Yadav, D. S.; Sharma, D.; Raad, B. R.; Bajaj, V. Superlattices Microstruct. 2016, 96, 36–46. doi:10.1016/j.spmi.2016.04.027 |

| 20. | Goswami, Y.; Ghosh, B.; Asthana, P. K. RSC Adv. 2014, 4, 10761–10765. doi:10.1039/C3RA46535G |

| 21. | Imen Abadi, R. M.; Sedigh Ziabari, S. A. Appl. Phys. A 2016, 122, 988. doi:10.1007/s00339-016-0530-9 |

| 22. | Raad, B. R.; Sharma, D.; Kondekar, P.; Nigam, K.; Yadav, D. S. IEEE Trans. Electron Devices 2016, 63, 3950–3957. doi:10.1109/TED.2016.2600621 |

| 23. | Yu, T.-Y.; Peng, L.-S.; Lin, C.-W.; Hsin, Y.-M. Microelectron. Reliab. 2018, 83, 235–237. doi:10.1016/j.microrel.2017.05.017 |

| 24. | Raad, B. R.; Sharma, D.; Tirkey, S. Microelectron. Eng. 2018, 194, 79–84. doi:10.1016/j.mee.2018.03.007 |

| 25. | ATLAS User's manual device simulation software; Silvaco Int. Ltd.: Santa Clara, CA, U.S.A., 2012. |

| 18. | Ghosh, B.; Akram, M. W. IEEE Electron Device Lett. 2013, 34, 584–586. doi:10.1109/LED.2013.2253752 |

| 25. | ATLAS User's manual device simulation software; Silvaco Int. Ltd.: Santa Clara, CA, U.S.A., 2012. |

| 15. | Djeffal, F.; Ferhati, H.; Bentrcia, T. Superlattices Microstruct. 2016, 90, 132–140. doi:10.1016/j.spmi.2015.09.041 |

| 16. | Lee, C.-W.; Afzalian, A.; Akhavan, N. D.; Yan, R.; Ferain, I.; Colinge, J.-P. Appl. Phys. Lett. 2009, 94, 053511. doi:10.1063/1.3079411 |

| 17. | Colinge, J.-P.; Lee, C.-W.; Afzalian, A.; Akhavan, N. D.; Yan, R.; Ferain, I.; Razavi, P.; Neill, B. N. O.; Blake, A.; White, M.; Kelleher, A.-M.; Carthy, B.; Murphy, R. Nat. Nanotechnol. 2010, 5, 225–229. doi:10.1038/nnano.2010.15 |

| 14. | Chebaki, E.; Djeffal, F.; Ferhati, H.; Bentrcia, T. Superlattices Microstruct. 2016, 92, 80–91. doi:10.1016/j.spmi.2016.02.009 |

| 15. | Djeffal, F.; Ferhati, H.; Bentrcia, T. Superlattices Microstruct. 2016, 90, 132–140. doi:10.1016/j.spmi.2015.09.041 |

| 16. | Lee, C.-W.; Afzalian, A.; Akhavan, N. D.; Yan, R.; Ferain, I.; Colinge, J.-P. Appl. Phys. Lett. 2009, 94, 053511. doi:10.1063/1.3079411 |

| 17. | Colinge, J.-P.; Lee, C.-W.; Afzalian, A.; Akhavan, N. D.; Yan, R.; Ferain, I.; Razavi, P.; Neill, B. N. O.; Blake, A.; White, M.; Kelleher, A.-M.; Carthy, B.; Murphy, R. Nat. Nanotechnol. 2010, 5, 225–229. doi:10.1038/nnano.2010.15 |

| 25. | ATLAS User's manual device simulation software; Silvaco Int. Ltd.: Santa Clara, CA, U.S.A., 2012. |

© 2018 Ferhati et al.; licensee Beilstein-Institut.

This is an Open Access article under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/4.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

The license is subject to the Beilstein Journal of Nanotechnology terms and conditions: (https://www.beilstein-journals.org/bjnano)