Abstract

Since 2004 the field of graphene research has attracted increasing interest worldwide. Especially the integration of graphene into microelectronic devices has the potential for numerous applications. Therefore, we summarize the current knowledge on this aspect. Surveys show that considerable progress was made in the field of graphene synthesis. However, the central issue consists of the availability of techniques suitable for production for the deposition of graphene on dielectric substrates. Besides, the encapsulation of graphene for further processing while maintaining its properties poses a challenge. Regarding the graphene/metal contact intensive research was done and recently substantial advancements were made towards contact resistances applicable for electronic devices. Generally speaking the crucial issues for graphene integration are identified today and the corresponding research tasks can be clearly defined.

Introduction

Since the discovery of the electronic properties of graphene in 2004 [1] a lot of possible applications have been envisioned. Especially in the field of microelectronics graphene holds the promise for faster, more sensitive and even completely novel devices [2]. So, graphene was claimed as one possible material to overcome the foreseeable limits of silicon technology. The fascinating properties of graphene, such as extremely high charge carrier mobility of more than 200,000 cm2·V−1·s−1 [3], was consistently shown in academic research. For instance, a sheet of high-quality graphene sandwiched between two exfoliated single-crystalline hexagonal boron nitride (h-BN) sheets shows a charge carrier mobility of 200,000 cm2·V−1·s−1 [4], which is about 300 times higher than that of silicon. However, if graphene is integrated in real-world devices with the constraints of manufacturability, the properties of graphene and its devices dramatically degrade. The integration of graphene demands a paradigm shift for material integration concepts, in conventional semiconductors the materials properties are mostly determined by the bulk of the semiconductor, and the surface can be cleaned and modified without significantly affecting the materials properties. On the other hand graphene and other 2D materials consist only of surface and every surface modification changes the materials properties. This property allows the use of graphene as an environmental sensor, but is detrimental to fabricating stable devices. In the following review we highlighted the most crucial aspects of the integration of graphene into complementary metal-oxide semiconductor (CMOS) compatible electronic devices.

Review

1 Deposition of graphene

Graphene films can synthesized in numerous ways, such as mechanical exfoliation, liquid-phase exfoliation, assembly of tailored precursor molecules, epitaxy on silicon carbide or chemical vapor deposition (CVD) on catalytic metals [5]. Besides meeting the requirements of film quality and cost, the scalability to 200 or 300 mm wafer sizes is crucial for being suitable for industrial production. Currently, the highest-quality graphene synthesis method that fulfills these constraints is graphene CVD on copper substrates [4,6]. However, for building electronic devices graphene typically has to be placed on an insulating substrate. Hence the graphene films have to be transferred from their growth substrate to the device substrate. In the past several methods have been proposed [7], which can be grouped into the following categories.

1.1 Ex situ transfer

The CVD growth substrate can either be a copper foil, which is most commonly used, or a Cu film deposited by physical vapor deposition (PVD) on a silicon wafer substrate with a diffusion barrier between the silicon substrate and the Cu film. The first approach allows for the production of very large graphene films on a polymer carrier foil even in a roll-to-roll system [8,9]. The second approach is obviously more wafer-level compatible, but at deposition temperatures around 1000 °C, even with diffusion barrier, it suffers from the diffusion of Si from the substrate towards the Cu surface generating holes in the graphene film. Decreasing the deposition temperature to below 800 °C can improve the defect level but cannot completely eliminate it [10]. Also the transfer onto a dielectric substrate wafer for device fabrication in a wafer bonder tool has not been established yet. Both techniques have in common that the strongly different thermal expansion coefficients of graphene (−6 × 10−6 K−1) [11,12] and the copper substrate (16.5 × 10−6 K−1) [13] typically lead to wrinkles and cracks in the graphene film. Lowering the deposition temperature would be also beneficial here. Several approaches have been reported [14-18], but have not been shown yet to yield an acceptable graphene quality.

In history, the first transfer technique for graphene films from the CVD growth substrate was the ex situ transfer by reinforcing the graphene layer with a polymer film, e.g., poly(methyl methacrylate) (PMMA), and etching off the Cu growth substrate. There are several options for subsequent graphene deposition onto the final substrates discussed in [19] (Figure 1).

![[2190-4286-8-107-1]](/bjnano/content/figures/2190-4286-8-107-1.png?scale=2.0&max-width=1024&background=FFFFFF)

Figure 1: Schematic illustration of dry and wet transfer processes. (a) Dry transfer onto shallow depressions. Wet transfer onto (b) perforated substrates and (c) flat substrates. The boxes with dashed lines in (a3) and (a4) show magnified views. Reprinted with permission from [19], copyright 2011 American Chemical Society.

Figure 1: Schematic illustration of dry and wet transfer processes. (a) Dry transfer onto shallow depressions...

Focusing on wafer-level processes, the metal underetch times are rather long, even when the graphene film is patterned to provide distributed access for the etch medium. A technique that copes with this problem is the so-called “bubble transfer”, which uses the generation of electrochemically generated hydrogen bubbles at the graphene–metal interface to release the polymer-supported graphene film without the need of lengthy underetching [20,21]. Nevertheless, defects generated by the hydrogen bubbles have to be considered.

After release of the polymer-reinforced graphene film from the growth substrate the graphene is contacted with the dielectric device substrate, either using a liquid medium (“wet transfer”) [19] or a flexible stamp [19] (“dry transfer”). Due to its high adhesion energy on hydrophilic substrates such as SiO2 (450 mJ/m2) [22] supported by the formation of a water layer [23] graphene attaches to the substrate and, after drying, the supporting polymer is removed by using a solvent. However, as water molecules should completely be removed from the graphene–substrate interface in order to reduce doping effects, the use of hydrophobic substrates is of high interest.

1.2 In situ transfer

The ex situ transfer approach suffers from the potential introduction of defects between the graphene film and the device substrate as well as from the generation of cracks in the graphene film itself [24]. For this reason, a preferable technique would be the graphene deposition on the final device substrate itself. As current methods are using a catalytic metal layer, one approach is the in situ removal of the metal layer between graphene and dielectric substrate by wet etching. In order to attach the graphene film to the substrate an additional adhesion mechanism has to be involved. One approach is the use of capillary forces introduced by gas bubbles released from the substrate during Cu wet etch [25]. The resulting graphene quality is usually better than produced by ex situ transfer. However, this approach suffers from a limited Cu film thickness, which can lead to voids in the catalytic growth layer due to Cu evaporation and stress migration during CVD growth. As already mentioned above the long underetch time causes problems.

1.3 Direct deposition

The ideal procedure includes the direct deposition of graphene on the dielectric device substrate without a catalytic metal layer in between. Two concepts can be characterized by the type of metal removal. The first approach is based on the removal of the metal layer during the CVD process by evaporation [26] or agglomeration [27]. However, the evaporation process lowers the graphene quality. The other approach is the implementation of a dissolution–precipitation mechanism of carbon in nickel at high temperatures and removing the metal after the deposition process. Here carbon is introduced into Ni by deposition of C/Ni sandwich layers or by ion implantation [28] or dissolution of carbon into nickel in a plasma-enhanced CVD process [29]. Upon heating up to about 1000 °C carbon dissolves in Ni with a substantial solubility and during cooling down it segregates to the Ni–substrate interface where it precipitates as graphene. After etching off the nickel, the graphene film is exposed. The complete process sequence is shown in Figure 2 [29].

![[2190-4286-8-107-2]](/bjnano/content/figures/2190-4286-8-107-2.png?scale=2.0&max-width=1024&background=FFFFFF)

Figure 2: Schematic illustration of the basic approach for the method of direct growth of graphene on a SiO2 surface. (a) A thin Ni film is deposited on a SiO2/Si substrate. (b) Plasma CVD is performed. (c) Carbon atoms diffuse into the Ni film, and graphene is preferentially grown along the interface between the Ni and SiO2 layers. (d) Graphene on a SiO2/Si substrate is realized by removing the Ni film using a chemical etching technique. Reprinted with permission from [29], copyright 2012 American Chemical Society.

Figure 2: Schematic illustration of the basic approach for the method of direct growth of graphene on a SiO2 ...

By choosing the appropriate temperature profile and C/Ni ratio the number of graphene layers can be controlled. However, process control is difficult and Ni grain boundaries can lead to an inhomogeneous thickness distribution of the graphene layer. A similar approach utilizes the diffusion of carbon species from a CVD atmosphere along grain boundaries through a copper film to the underlying substrate [30]. As there is no significant solubility of carbon in copper, the film formation is expected to be very inhomogeneous. Alternatively Cu is used as catalytic material to convert a self-assembled monolayer as carbon source at the Cu/SiO2 substrate to graphene [31].

A newer procedure is the use of a suitable growth substrate that is compatible with device fabrication. Such a suitable substrate material is germanium [32,33] but only a limited choice of electronic devices can make use of Ge. Thus the transfer of graphene from this growth substrate, preferably using etch-free methods due to high substrate cost [32], is an interesting option.

2 Intrinsic properties

The quality of the graphene material itself is a result of the growth and transfer process and can be influenced by several intrinsic properties.

2.1 Grain boundaries

One property is the density of defects. In the case of good quality graphene it is mainly determined by the density of grain boundaries between the single-crystalline domains [34]. If a grain boundary lies inside the active region of a graphene device it reduces the device performance by locally changing the charge carrier mobility. Several studies have been conducted on this topic [35,36], but the impact on manufacturability is still not very clear. However, there is continuous improvement towards large crystallite sizes in the millimeter range [37,38].

2.2 Contamination

Another important intrinsic property of graphene is the amount of contaminations from the synthesis and transfer process. The synthesis process mainly introduces metallic contaminations typically in the range of 1013 to 1014 atoms·cm−2, which corresponds to every tenth to hundredth atom in a monolayer. The main contamination is Cu from the CVD process, but also Fe is found in remarkable amounts. Several cleaning processes have been evaluated, but no substantial contamination removal could be achieved [39]. These metal contamination levels do not only lead to difficult integration into CMOS process lines (the typical upper control limit is in the range of 1010 to 1011 atoms·cm−1, depending on the metal type and technology). They also are influencing the graphene properties by charge-transfer doping [40,41]. The second main contamination source, polymer residues, typically originates in the transfer process from incompletely removed supporting polymer layers such as PMMA. Though, these residues usually can be removed by an appropriate vacuum annealling [42].

3 Substrate interactions

Because graphene consists only of surface, every interaction with its environment changes its properties. Hence, also the dielectric device substrate on which a graphene layer is deposited has an influence on properties of graphene such as charge carrier mobility and density. There is a large spread of reported charge carrier mobilities for graphene on different substrates, such as 4,400–17,000 cm2·V−1·s−1 for SiO2 [43] in contrast to 25,000–140,000 cm2·V−1·s−1 for h-BN [44]. Besides the formation of chemical bonds, mainly two mechanisms describe the graphene–substrate interactions, charge-transfer doping and the introduction of strain on the nanoscale. Also, the surface functionalization, e.g., of SiO2 with hexamethyldisilazane (HMDS) has a strong influence on the charge carrier mobility (Figure 3) [45].

![[2190-4286-8-107-3]](/bjnano/content/figures/2190-4286-8-107-3.png?scale=2.0&max-width=1024&background=FFFFFF)

Figure 3: Schematic illustration of the mobility (experiment) as a function of the ratio between CxHy size and silanol group density (expected). Reprinted with permission from [45], copyright 2011 AIP Publishing.

Figure 3: Schematic illustration of the mobility (experiment) as a function of the ratio between CxHy size an...

3.1 Doping

Charges in a dielectric substrate can be introduced by foreign atoms and dangling bonds as well as by mobile ions. The doping of supported graphene samples on different substrates is influenced through these charges due to image-charge formation. SiO2 and h-BN shows hole doping in graphene in the range of 1012 to 1013 cm−2 [46,47], surface-functionalized SiO2 with HMDS shows a lower hole doping of approximately 1.25 × 1012 cm−2 [48]. Pre-treatment of the surface has a large influence on doping and therefore on the mobility in graphene sheets. Plasma-treated SiO2 surfaces reveal reduced hole doping because of the absence of organic residues, HF-treated SiO2 shows higher hole doping values due to fluorine dangling bonds. Also water and hydrocarbon molecules adsorbed on the SiO2 surface show a significant effect [45].

3.2 Nanostrain

Another type of substrate–graphene interaction is the introduction of local strain induced by substrate roughness on the nanometer scale. The resulting deformation of graphene leads to degradation of the charge carrier mobility. Graphene on flat surfaces like h-BN and SiO2 show a compressive strain of approximately −0.1% [49]. On epitaxial germanium(001) with a higher surface roughness there is a higher compressive strain in the range between −0.37% and −0.25% [33]. Thus, it is crucial to provide substrates as smooth as possible for graphene integration.

4 Encapsulation

In order to protect the graphene layer from environmental influences during further device processing an encapsulation with protective material is required. As mentioned above, the interaction of graphene with neighboring materials has to be minimized. So, a suitable material must fulfill the requirement of acting as a diffusion barrier against humidity, chemicals and gases during further processing. In addition, it has to be deposited using a process with minimal influence on graphene, e.g., high-temperature or plasma-CVD processes are to avoided. Encapsulation with exfoliated single-crystalline h-BN layers yields excellent results [4], but this is not a production-relevant approach. A material that is available in mass-production quantities and fulfills both mentioned requirements is aluminum oxide deposited by atomic-layer deposition (ALD). It was demonstrated that graphene encapsulated in Al2O3 could be passivated (Figure 4) and was stable for a longer period of time under ambient conditions [50].

![[2190-4286-8-107-4]](/bjnano/content/figures/2190-4286-8-107-4.png?scale=2.0&max-width=1024&background=FFFFFF)

Figure 4: (a) Schematic showing the layers of material used in fabrication of a back-gated graphene RF-transistor. (b) Transfer function of the transistor before and after passivation. Reproduced with permission from [50], copyright 2015 The Royal Society of Chemistry.

Figure 4: (a) Schematic showing the layers of material used in fabrication of a back-gated graphene RF-transi...

The main problem of growing Al2O3 by ALD is to obtain a continuous nucleation layer on graphene to start the deposition. To solve this problem several approaches are proposed. One solution is the deposition of a few nanometers thin Al layer on graphene and subsequently oxidizing it in air to generate a thin start layer for a subsequent ALD process depositing several tens of nanometers of Al2O3 [50]. Further there is an adapted nucleation process using water and trimethylaluminium (TMA) as precursors at untypically low temperatures down to 80 °C [51].

As little as possible interaction of graphene with the encapsulation materials is required to maintain the properties of graphene. In other words, this interaction is detrimental to the adhesion of graphene on the substrate and the encapsulation materials. The integrity of graphene devices is strongly affected by the adhesion strength. Adhesion strength generally depends on adhesion energy, device area and externally induced strain, e.g., from metal and dielectric layers. Figure 5 depicts our experimental findings on the probability of delamination of a high-k dielectric/nickel stack on graphene as a function of the graphene device area. The 200 nm thick Ni film was introduced as a layer to provoke delamination through tensile stress. The existence of a distinctive device area threshold for delamination can clearly be seen. This indicates that delamination effects should be manageable with respect to device manufacturing.

![[2190-4286-8-107-5]](/bjnano/content/figures/2190-4286-8-107-5.png?scale=2.0&max-width=1024&background=FFFFFF)

Figure 5: Probability of delamination of a high-k dielectric/Ni stack on graphene devices as a function of the device area. The data are extracted from 520 devices in total.

Figure 5: Probability of delamination of a high-k dielectric/Ni stack on graphene devices as a function of th...

5 Contacts

Because the performance of an electronic device, e.g., a transistor, is strongly affected by parasitic effects such as contact resistances (the contact resistance should not exceed 10% of the channel resistance), this issue is of enormous importance, especially for short-channel devices. Numerous studies have been published during the last few years on the understanding and improvement of graphene–metal contacts, reporting contact resistivity values in a wide range from several ohm-micrometers to several hundred thousand ohm-micrometers. Metal contacts can interact with graphene in different ways [52], as shown in Figure 6.

![[2190-4286-8-107-6]](/bjnano/content/figures/2190-4286-8-107-6.png?scale=2.0&max-width=1024&background=FFFFFF)

Figure 6: Obtained Rc·contact width values as a function of the contact-metal work function (WF) and increasing metal reactivity. A clear trend can be observed correlating the high measured Rc values with the most reactive metals (Ni, Ti). Reprinted with permission from [52], copyright 2015 AIP Publishing.

Figure 6: Obtained Rc·contact width values as a function of the contact-metal work function (WF) and increasi...

Metals physisorbed on graphene cause charge-transfer-induced doping of the graphene sheet because of the difference in work function values [53]. Metals chemisorbed on graphene are open a band gap in graphene. Both mechanisms result an increased contact resistance. Besides through choosing an appropriate metal, the contact resistance can be improved by thorough interface engineering [54] and applying an electrical field under the contacts to adjust the Fermi energy [55,56]. With respect to CMOS integration it seems that even CMOS-compatible contact metals such as Ni are yielding reasonable contact resistances [57]. The most promising contact-geometry approach is the formation of a one-dimensional contact, contacting the graphene film from the side [58,59] according to Figure 7. With this configuration contact resistances as low as 100 Ω·μm can be achieved.

![[2190-4286-8-107-7]](/bjnano/content/figures/2190-4286-8-107-7.png?scale=2.0&max-width=1024&background=FFFFFF)

Figure 7: Schematic of the edge-contact fabrication process. Reprinted with permission from [58], copyright 2013 AAAS.

Figure 7: Schematic of the edge-contact fabrication process. Reprinted with permission from [58], copyright 2013 ...

6 General integration issues

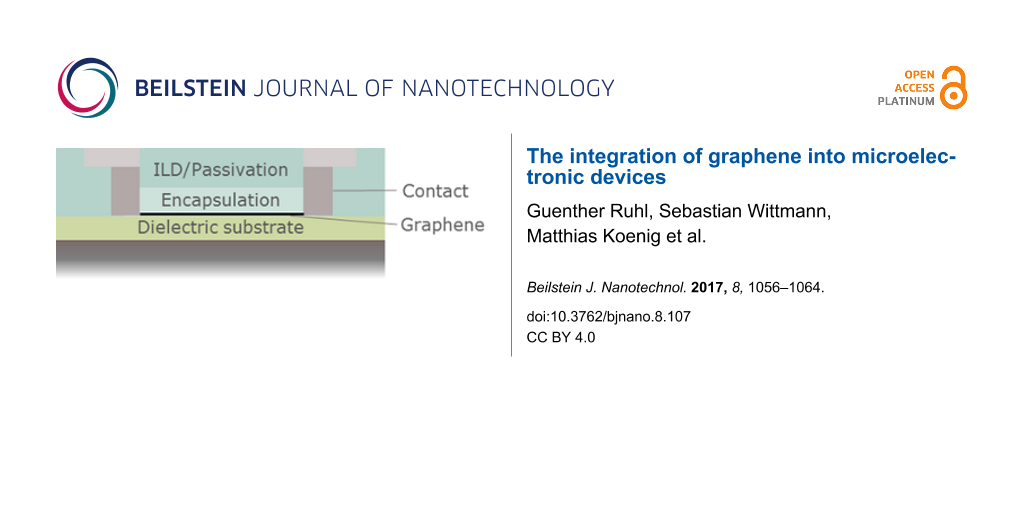

Referring to the aspects mentioned above, the currently most suitable integration scheme includes the utilization of the encapsulation layer as etching hardmask for structuring the graphene layer in order to avoid a contamination of graphene by following lithography steps. One method utilizes a one-step plasma-etch process with low selectivity to the underlying dielectric substrate to etch the encapsulation/hardmask layer and the underlying graphene simultaneously. An alternative approach applies two consecutive steps to etch the hardmask by a selective plasma etch or wet etch, followed by a second highly substrate-selective oxygen-plasma etch step to remove graphene. Both methods are schematically depicted in Figure 8a. The first method seems to be more suitable for the fabrication of side contacts. However, it needs to be ensured that the etch polymer residues are removed thoroughly to enable optimal contact formation. Of course lateral underetch effects must be avoided. In the next step the contact metal is deposited and structured with standard processes followed by inter-layer dielectric and passivation layers. The general device schematic is depicted in Figure 8b.

![[2190-4286-8-107-8]](/bjnano/content/figures/2190-4286-8-107-8.png?scale=2.0&max-width=1024&background=FFFFFF)

Figure 8: (a) Schematic of the final side-contact hole cross-section after a one-step non-selective etch process and a two-step selective etch process. (b) General schematic of the integrated device comprising side contacts.

Figure 8: (a) Schematic of the final side-contact hole cross-section after a one-step non-selective etch proc...

Because graphene as a carbon allotrope can react with other materials at high temperatures forming, e.g., metal carbides or carbon dioxide, care has to be taken that the subsequent processing steps do not employ temperatures exceeding 500 °C. The favorite solution to this issue is the so-called graphene-last approach in which graphene devices are formed in the metallization levels of a CMOS device [60].

Conclusion

The integration of graphene into CMOS-compatible electronic devices poses a lot of challenges when mass-production aspects are taken into account. An appropriate graphene quality can be produced by CVD on Cu substrates. Unsolved issues are the influence of grain boundaries and the reduction of metallic contamination. However, the synthesized graphene films have to be transferred to a dielectric substrate forming the device. This transfer process is critical as it is sensitive to defects, such as particles, cracks and wrinkles that degrade the graphene quality. Direct deposition methods on dielectric substrates exist, but do not yield a sufficient quality yet. We assume that this improvement of the deposition complex is crucial for commercializing graphene for microelectronics. Additionally, substrate interactions are strongly degrading the graphene quality. Hexagonal boron nitride has been identified as the ideal substrate material, but it is not available yet in the required quality for producing wafers. In order to obtain manufacturable graphene devices in the near future, established materials, such as SiO2, have to be adapted, even if the best possible graphene performance cannot be achieved. The encapsulation of graphene by Al2O3 seems to be solvable in the near future, as well as the formation of low-resistance graphene metal contacts. From today’s perspective the main issues for wafer-scale integration of graphene are well known, and the future of graphene (and other two-dimensional materials, namely transition metal dichalkogenides) in microelectronics depends on the successful solution of these problems.

References

-

Novoselov, K. S.; Geim, A. K.; Morozov, S. V.; Jiang, D.; Zhang, Y.; Dubonos, S. V.; Grigorieva, I. V.; Firsov, A. A. Science 2004, 306, 666. doi:10.1126/science.1102896

Return to citation in text: [1] -

Ferrari, A. C.; Bonaccorso, F.; Fal’ko, V.; Novoselov, K. S.; Roche, S.; Bøggild, P.; Borini, S.; Koppens, F. H. L.; Palermo, V.; Pugno, N.; Garrido, J. A.; Sordan, R.; Bianco, A.; Ballerini, L.; Prato, M.; Lidorikis, E.; Kivioja, J.; Marinelli, C.; Ryhänen, T.; Morpurgo, A.; Coleman, J. N.; Nicolosi, V.; Colombo, L.; Fert, A.; Garcia-Hernandez, M.; Bachtold, A.; Schneider, G. F.; Guinea, F.; Dekker, C.; Barbone, M.; Sun, Z.; Galiotis, C.; Grigorenko, A. N.; Konstantatos, G.; Kis, A.; Katsnelson, M.; Vandersypen, L.; Loiseau, A.; Morandi, V.; Neumaier, D.; Treossi, E.; Pellegrini, V.; Polini, M.; Tredicucci, A.; Williams, G. M.; Hong, B. H.; Ahn, J.-H.; Kim, J. M.; Zirath, H.; van Wees, B. J.; van der Zant, H.; Occhipinti, L.; Di Matteo, A.; Kinloch, I. A.; Seyller, T.; Quesnel, E.; Feng, X.; Teo, K.; Rupesinghe, N.; Hakonen, P.; Neil, S. R. T.; Tannock, Q.; Löfwander, T.; Kinaret, J. Nanoscale 2015, 7, 4598. doi:10.1039/C4NR01600A

Return to citation in text: [1] -

Bolotin, K. I.; Sikes, K. J.; Jiang, Z.; Klima, M.; Fudenberg, G.; Hone, J.; Kim, P.; Stormer, H. L. Solid State Commun. 2008, 146, 351. doi:10.1016/j.ssc.2008.02.024

Return to citation in text: [1] -

Banszerus, L.; Schmitz, M.; Engels, S.; Dauber, J.; Oellers, M.; Haupt, F.; Watanabe, K.; Taniguchi, T.; Beschoten, B.; Stampfer, C. Sci. Adv. 2015, 1, e1500222. doi:10.1126/sciadv.1500222

Return to citation in text: [1] [2] [3] -

Novoselov, K. S.; Fal'ko, V. I.; Colombo, L.; Gellert, P. R.; Schwab, M. G.; Kim, K. Nature 2012, 490, 192. doi:10.1038/nature11458

Return to citation in text: [1] -

Li, X.; Colombo, L.; Ruoff, R. S. Adv. Mater. 2016, 28, 6247. doi:10.1002/adma.201504760

Return to citation in text: [1] -

Kang, J.; Shin, D.; Bae, S.; Hong, B. H. Nanoscale 2012, 4, 5527. doi:10.1039/c2nr31317k

Return to citation in text: [1] -

Kim, K. S.; Zhao, Y.; Jang, H.; Lee, S. Y.; Kim, J. M.; Kim, K. S.; Ahn, J.-H.; Kim, P.; Choi, J.-Y.; Hong, B. H. Nature 2009, 457, 706. doi:10.1038/nature07719

Return to citation in text: [1] -

Bae, S.; Kim, H.; Lee, Y.; Xu, X.; Park, J.-S.; Zheng, Y.; Balakrishnan, J.; Lei, T.; Ri Kim, H.; Song, Y. I.; Kim, Y.-J.; Kim, K. S.; Özyilmaz, B.; Ahn, J.-H.; Hong, B. H.; Iijima, S. Nat. Nanotechnol. 2010, 5, 574. doi:10.1038/nnano.2010.132

Return to citation in text: [1] -

König, M.; Ruhl, G.; Batke, J.-M.; Lemme, M. C. Nanoscale 2016, 8, 15490. doi:10.1039/C6NR03954E

Return to citation in text: [1] -

Jiang, J.-W.; Wang, J.-S.; Li, B. Phys. Rev. B 2009, 80, 205429. doi:10.1103/PhysRevB.80.205429

Return to citation in text: [1] -

Yoon, D.; Son, Y.-W.; Cheong, H. Nano Lett. 2011, 11, 3227. doi:10.1021/nl201488g

Return to citation in text: [1] -

CRC Handbook of Chemistry and Physics, 92nd Edition. https://www.crcpress.com/CRC-Handbook-of-Chemistry-and-Physics-92nd-Edition/Haynes/p/book/9781439855126 (accessed Jan 18, 2017).

Return to citation in text: [1] -

Lee, C. S.; Baraton, L.; He, Z.; Maurice, J.-L.; Chaigneau, M.; Pribat, D.; Cojocaru, C. S. Proc. SPIE 2010, 7761, 77610P. doi:10.1117/12.861866

Return to citation in text: [1] -

Terasawa, T.; Saiki, K. Carbon 2012, 50, 869. doi:10.1016/j.carbon.2011.09.047

Return to citation in text: [1] -

Li, Z.; Wu, P.; Wang, C.; Fan, X.; Zhang, W.; Zhai, X.; Zeng, C.; Li, Z.; Yang, J.; Hou, J. ACS Nano 2011, 5, 3385. doi:10.1021/nn200854p

Return to citation in text: [1] -

Zhang, B.; Lee, W. H.; Piner, R.; Kholmanov, I.; Wu, Y.; Li, H.; Ji, H.; Ruoff, R. S. ACS Nano 2012, 6, 2471. doi:10.1021/nn204827h

Return to citation in text: [1] -

Jiang, L.; Niu, T.; Lu, X.; Dong, H.; Chen, W.; Liu, Y.; Hu, W.; Zhu, D. J. Am. Chem. Soc. 2013, 135, 9050. doi:10.1021/ja4031825

Return to citation in text: [1] -

Suk, J. W.; Kitt, A.; Magnuson, C. W.; Hao, Y.; Ahmed, S.; An, J.; Swan, A. K.; Goldberg, B. B.; Ruoff, R. S. ACS Nano 2011, 5, 6916. doi:10.1021/nn201207c

Return to citation in text: [1] [2] [3] [4] -

de la Rosa, C. J. L.; Lindvall, N.; Cole, M. T.; Nam, Y.; Löffler, M.; Olsson, E.; Yurgens, A. Appl. Phys. Lett. 2013, 102, 22101. doi:10.1063/1.4775583

Return to citation in text: [1] -

Gao, L.; Ren, W.; Xu, H.; Jin, L.; Wang, Z.; Ma, T.; Ma, L.-P.; Zhang, Z.; Fu, Q.; Peng, L.-M.; Bao, X.; Cheng, H.-M. Nat. Commun. 2012, 3, 699. doi:10.1038/ncomms1702

Return to citation in text: [1] -

Koenig, S. P.; Boddeti, N. G.; Dunn, M. L.; Bunch, J. S. Nat. Nanotechnol. 2011, 6, 543. doi:10.1038/nnano.2011.123

Return to citation in text: [1] -

Temmen, M.; Ochedowski, O.; Schleberger, M.; Reichling, M.; Bollmann, T. R. J. New J. Phys. 2014, 16, 053039. doi:10.1088/1367-2630/16/5/053039

Return to citation in text: [1] -

Liang, X.; Sperling, B. A.; Calizo, I.; Cheng, G.; Hacker, C. A.; Zhang, Q.; Obeng, Y.; Yan, K.; Peng, H.; Li, Q.; Zhu, X.; Yuan, H.; Hight Walker, A. R.; Liu, Z.; Peng, L.; Richter, C. A. ACS Nano 2011, 5, 9144. doi:10.1021/nn203377t

Return to citation in text: [1] -

Gao, L.; Ni, G.-X.; Liu, Y.; Liu, B.; Castro Neto, A. H.; Loh, K. P. Nature 2014, 505, 190. doi:10.1038/nature12763

Return to citation in text: [1] -

Ismach, A.; Druzgalski, C.; Penwell, S.; Schwartzberg, A.; Zheng, M.; Javey, A.; Bokor, J.; Zhang, Y. Nano Lett. 2010, 10, 1542. doi:10.1021/nl9037714

Return to citation in text: [1] -

Banno, K.; Mizuno, M.; Fujita, K.; Kubo, T.; Miyoshi, M.; Egawa, T.; Soga, T. Appl. Phys. Lett. 2013, 103, 082112. doi:10.1063/1.4818342

Return to citation in text: [1] -

Kim, J.; Lee, G.; Kim, J. Appl. Phys. Lett. 2015, 107, 033104. doi:10.1063/1.4926605

Return to citation in text: [1] -

Kato, T.; Hatakeyama, R. ACS Nano 2012, 6, 8508. doi:10.1021/nn302290z

Return to citation in text: [1] [2] [3] -

Su, C.-Y.; Lu, A.-Y.; Wu, C.-Y.; Li, Y.-T.; Liu, K.-K.; Zhang, W.; Lin, S.-Y.; Juang, Z.-Y.; Zhong, Y.-L.; Chen, F.-R.; Li, L.-J. Nano Lett. 2011, 11, 3612. doi:10.1021/nl201362n

Return to citation in text: [1] -

Shin, H.-J.; Choi, W. M.; Yoon, S.-M.; Han, G. H.; Woo, Y. S.; Kim, E. S.; Chae, S. J.; Li, X.-S.; Benayad, A.; Loc, D. D.; Gunes, F.; Lee, Y. H.; Choi, J.-Y. Adv. Mater. 2011, 23, 4392. doi:10.1002/adma.201102526

Return to citation in text: [1] -

Lee, J.-H.; Lee, E. K.; Joo, W.-J.; Jang, Y.; Kim, B.-S.; Lim, J. Y.; Choi, S.-H.; Ahn, S. J.; Ahn, J. R.; Park, M.-H.; Yang, C.-W.; Choi, B. L.; Hwang, S.-W.; Whang, D. Science 2014, 344, 286. doi:10.1126/science.1252268

Return to citation in text: [1] [2] -

Pasternak, I.; Wesolowski, M.; Jozwik, I.; Lukosius, M.; Lupina, G.; Dabrowski, P.; Baranowski, J. M.; Strupinski, W. Sci. Rep. 2016, 6, 21773. doi:10.1038/srep21773

Return to citation in text: [1] [2] -

Cummings, A. W.; Duong, D. L.; Nguyen, V. L.; Van Tuan, D.; Kotakoski, J.; Barrios Vargas, J. E.; Lee, Y. H.; Roche, S. Adv. Mater. 2014, 26, 5079. doi:10.1002/adma.201401389

Return to citation in text: [1] -

Duong, D. L.; Han, G. H.; Lee, S. M.; Gunes, F.; Kim, E. S.; Kim, S. T.; Kim, H.; Ta, Q. H.; So, K. P.; Yoon, S. J.; Chae, S. J.; Jo, Y. W.; Park, M. H.; Chae, S. H.; Lim, S. C.; Choi, J. Y.; Lee, Y. H. Nature 2012, 490, 235. doi:10.1038/nature11562

Return to citation in text: [1] -

Song, H. S.; Li, S. L.; Miyazaki, H.; Sato, S.; Hayashi, K.; Yamada, A.; Yokoyama, N.; Tsukagoshi, K. Sci. Rep. 2012, 2, 337. doi:10.1038/srep00337

Return to citation in text: [1] -

Mohsin, A.; Liu, L.; Liu, P.; Deng, W.; Ivanov, I. N.; Li, G.; Dyck, O. E.; Duscher, G.; Dunlap, J. R.; Xiao, K.; Gu, G. ACS Nano 2013, 7, 8924. doi:10.1021/nn4034019

Return to citation in text: [1] -

Chen, S.; Ji, H.; Chou, H.; Li, Q.; Li, H.; Suk, J. W.; Piner, R.; Liao, L.; Cai, W.; Ruoff, R. S. Adv. Mater. 2013, 25, 2062. doi:10.1002/adma.201204000

Return to citation in text: [1] -

Lupina, G.; Kitzmann, J.; Costina, I.; Lukosius, M.; Wenger, C.; Wolff, A.; Vaziri, S.; Östling, M.; Pasternak, I.; Krajewska, A.; Strupinski, W.; Kataria, S.; Gahoi, A.; Lemme, M. C.; Ruhl, G.; Zoth, G.; Luxenhofer, O.; Mehr, W. ACS Nano 2015, 9, 4776. doi:10.1021/acsnano.5b01261

Return to citation in text: [1] -

Subrahmanyam, K. S.; Manna, A. K.; Pati, S. K.; Rao, C. N. R. Chem. Phys. Lett. 2010, 497, 70. doi:10.1016/j.cplett.2010.07.091

Return to citation in text: [1] -

Pi, K.; McCreary, K. M.; Bao, W.; Han, W.; Chiang, Y. F.; Li, Y.; Tsai, S.-W.; Lau, C. N.; Kawakami, R. K. Phys. Rev. B 2009, 80, 075406. doi:10.1103/PhysRevB.80.075406

Return to citation in text: [1] -

Pirkle, A.; Chan, J.; Venugopal, A.; Hinojos, D.; Magnuson, C. W.; McDonnell, S.; Colombo, L.; Vogel, E. M.; Ruoff, R. S.; Wallace, R. M. Appl. Phys. Lett. 2011, 99, 122108. doi:10.1063/1.3643444

Return to citation in text: [1] -

Hong, X.; Zou, K.; Zhu, J. Phys. Rev. B 2009, 80, 241415. doi:10.1103/PhysRevB.80.241415

Return to citation in text: [1] -

Dean, C. R.; Young, A. F.; Meric, I.; Lee, C.; Wang, L.; Sorgenfrei, S.; Watanabe, K.; Taniguchi, T.; Kim, P.; Shepard, K. L.; Hone, J. Nat. Nanotechnol. 2010, 5, 722. doi:10.1038/nnano.2010.172

Return to citation in text: [1] -

Nagashio, K.; Yamashita, T.; Nishimura, T.; Kita, K.; Toriumi, A. J. Appl. Phys. 2011, 110, 024513. doi:10.1063/1.3611394

Return to citation in text: [1] [2] [3] -

Caridad, J. M.; Rossella, F.; Bellani, V.; Maicas, M.; Patrini, M.; Díez, E. J. Appl. Phys. 2010, 108, 084321. doi:10.1063/1.3500295

Return to citation in text: [1] -

Ahn, G.; Kim, H. R.; Ko, T. Y.; Choi, K.; Watanabe, K.; Taniguchi, T.; Hong, B. H.; Ryu, S. ACS Nano 2013, 7, 1533. doi:10.1021/nn305306n

Return to citation in text: [1] -

Lafkioti, M.; Krauss, B.; Lohmann, T.; Zschieschang, U.; Klauk, H.; v. Klitzing, K.; Smet, J. H. Nano Lett. 2010, 10, 1149. doi:10.1021/nl903162a

Return to citation in text: [1] -

Neumann, C.; Reichardt, S.; Venezuela, P.; Drögeler, M.; Banszerus, L.; Schmitz, M.; Watanabe, K.; Taniguchi, T.; Mauri, F.; Beschoten, B.; Rotkin, S. V.; Stampfer, C. Nat. Commun. 2015, 6, 8429. doi:10.1038/ncomms9429

Return to citation in text: [1] -

Sagade, A. A.; Neumaier, D.; Schall, D.; Otto, M.; Pesquera, A.; Centeno, A.; Elorza, A. Z.; Kurz, H. Nanoscale 2015, 7, 3558. doi:10.1039/C4NR07457B

Return to citation in text: [1] [2] [3] -

Aria, A. I.; Nakanishi, K.; Xiao, L.; Braeuninger-Weimer, P.; Sagade, A. A.; Alexander-Webber, J. A.; Hofmann, S. ACS Appl. Mater. Interfaces 2016, 8, 30564. doi:10.1021/acsami.6b09596

Return to citation in text: [1] -

Politou, M.; Asselberghs, I.; Radu, I.; Conard, T.; Richard, O.; Lee, C. S.; Martens, K.; Sayan, S.; Huyghebaert, C.; Tokei, Z.; De Gendt, S.; Heyns, M. Appl. Phys. Lett. 2015, 107, 153104. doi:10.1063/1.4933192

Return to citation in text: [1] [2] -

Gahoi, A.; Wagner, S.; Bablich, A.; Kataria, S.; Passi, V.; Lemme, M. C. Solid-State Electron. 2016, 125, 234. doi:10.1016/j.sse.2016.07.008

Return to citation in text: [1] -

Liu, W.; Wei, J.; Sun, X.; Yu, H. Crystals 2013, 3, 257. doi:10.3390/cryst3010257

Return to citation in text: [1] -

Wilmart, Q.; Inhofer, A.; Boukhicha, M.; Yang, W.; Rosticher, M.; Morfin, P.; Garroum, N.; Fève, G.; Berroir, J.-M.; Plaçais, B. Sci. Rep. 2016, 6, 21085. doi:10.1038/srep21085

Return to citation in text: [1] -

Cusati, T.; Fiori, G.; Gahoi, A.; Passi, V.; Fortunelli, A.; Lemme, M.; Iannaccone, G. Understanding the nature of metal-graphene contacts: A theoretical and experimental study. In Electron Devices Meeting (IEDM), 2015 IEEE International, Washington, DC, USA, Dec 7–9, 2015; IEEE, 2016; 12.7.1–12.7.4. doi:10.1109/IEDM.2015.7409686

Return to citation in text: [1] -

Chaves, F. A.; Jiménez, D.; Sagade, A. A.; Kim, W.; Riikonen, J.; Lipsanen, H.; Neumaier, D. 2D Mater. 2015, 2, 025006. doi:10.1088/2053-1583/2/2/025006

Return to citation in text: [1] -

Wang, L.; Meric, I.; Huang, P. Y.; Gao, Q.; Gao, Y.; Tran, H.; Taniguchi, T.; Watanabe, K.; Campos, L. M.; Muller, D. A.; Guo, J.; Kim, P.; Hone, J.; Shepard, K. L.; Dean, C. R. Science 2013, 342, 614. doi:10.1126/science.1244358

Return to citation in text: [1] [2] -

Leong, W. S.; Gong, H.; Thong, J. T. L. ACS Nano 2014, 8, 994. doi:10.1021/nn405834b

Return to citation in text: [1] -

Han, S.-J.; Garcia, A. V.; Oida, S.; Jenkins, K. A.; Haensch, W. Nat. Commun. 2014, 5, 3086. doi:10.1038/ncomms4086

Return to citation in text: [1]

| 30. | Su, C.-Y.; Lu, A.-Y.; Wu, C.-Y.; Li, Y.-T.; Liu, K.-K.; Zhang, W.; Lin, S.-Y.; Juang, Z.-Y.; Zhong, Y.-L.; Chen, F.-R.; Li, L.-J. Nano Lett. 2011, 11, 3612. doi:10.1021/nl201362n |

| 31. | Shin, H.-J.; Choi, W. M.; Yoon, S.-M.; Han, G. H.; Woo, Y. S.; Kim, E. S.; Chae, S. J.; Li, X.-S.; Benayad, A.; Loc, D. D.; Gunes, F.; Lee, Y. H.; Choi, J.-Y. Adv. Mater. 2011, 23, 4392. doi:10.1002/adma.201102526 |

| 32. | Lee, J.-H.; Lee, E. K.; Joo, W.-J.; Jang, Y.; Kim, B.-S.; Lim, J. Y.; Choi, S.-H.; Ahn, S. J.; Ahn, J. R.; Park, M.-H.; Yang, C.-W.; Choi, B. L.; Hwang, S.-W.; Whang, D. Science 2014, 344, 286. doi:10.1126/science.1252268 |

| 33. | Pasternak, I.; Wesolowski, M.; Jozwik, I.; Lukosius, M.; Lupina, G.; Dabrowski, P.; Baranowski, J. M.; Strupinski, W. Sci. Rep. 2016, 6, 21773. doi:10.1038/srep21773 |

| 42. | Pirkle, A.; Chan, J.; Venugopal, A.; Hinojos, D.; Magnuson, C. W.; McDonnell, S.; Colombo, L.; Vogel, E. M.; Ruoff, R. S.; Wallace, R. M. Appl. Phys. Lett. 2011, 99, 122108. doi:10.1063/1.3643444 |

| 43. | Hong, X.; Zou, K.; Zhu, J. Phys. Rev. B 2009, 80, 241415. doi:10.1103/PhysRevB.80.241415 |

| 39. | Lupina, G.; Kitzmann, J.; Costina, I.; Lukosius, M.; Wenger, C.; Wolff, A.; Vaziri, S.; Östling, M.; Pasternak, I.; Krajewska, A.; Strupinski, W.; Kataria, S.; Gahoi, A.; Lemme, M. C.; Ruhl, G.; Zoth, G.; Luxenhofer, O.; Mehr, W. ACS Nano 2015, 9, 4776. doi:10.1021/acsnano.5b01261 |

| 40. | Subrahmanyam, K. S.; Manna, A. K.; Pati, S. K.; Rao, C. N. R. Chem. Phys. Lett. 2010, 497, 70. doi:10.1016/j.cplett.2010.07.091 |

| 41. | Pi, K.; McCreary, K. M.; Bao, W.; Han, W.; Chiang, Y. F.; Li, Y.; Tsai, S.-W.; Lau, C. N.; Kawakami, R. K. Phys. Rev. B 2009, 80, 075406. doi:10.1103/PhysRevB.80.075406 |

| 35. | Duong, D. L.; Han, G. H.; Lee, S. M.; Gunes, F.; Kim, E. S.; Kim, S. T.; Kim, H.; Ta, Q. H.; So, K. P.; Yoon, S. J.; Chae, S. J.; Jo, Y. W.; Park, M. H.; Chae, S. H.; Lim, S. C.; Choi, J. Y.; Lee, Y. H. Nature 2012, 490, 235. doi:10.1038/nature11562 |

| 36. | Song, H. S.; Li, S. L.; Miyazaki, H.; Sato, S.; Hayashi, K.; Yamada, A.; Yokoyama, N.; Tsukagoshi, K. Sci. Rep. 2012, 2, 337. doi:10.1038/srep00337 |

| 37. | Mohsin, A.; Liu, L.; Liu, P.; Deng, W.; Ivanov, I. N.; Li, G.; Dyck, O. E.; Duscher, G.; Dunlap, J. R.; Xiao, K.; Gu, G. ACS Nano 2013, 7, 8924. doi:10.1021/nn4034019 |

| 38. | Chen, S.; Ji, H.; Chou, H.; Li, Q.; Li, H.; Suk, J. W.; Piner, R.; Liao, L.; Cai, W.; Ruoff, R. S. Adv. Mater. 2013, 25, 2062. doi:10.1002/adma.201204000 |

| 32. | Lee, J.-H.; Lee, E. K.; Joo, W.-J.; Jang, Y.; Kim, B.-S.; Lim, J. Y.; Choi, S.-H.; Ahn, S. J.; Ahn, J. R.; Park, M.-H.; Yang, C.-W.; Choi, B. L.; Hwang, S.-W.; Whang, D. Science 2014, 344, 286. doi:10.1126/science.1252268 |

| 34. | Cummings, A. W.; Duong, D. L.; Nguyen, V. L.; Van Tuan, D.; Kotakoski, J.; Barrios Vargas, J. E.; Lee, Y. H.; Roche, S. Adv. Mater. 2014, 26, 5079. doi:10.1002/adma.201401389 |

| 44. | Dean, C. R.; Young, A. F.; Meric, I.; Lee, C.; Wang, L.; Sorgenfrei, S.; Watanabe, K.; Taniguchi, T.; Kim, P.; Shepard, K. L.; Hone, J. Nat. Nanotechnol. 2010, 5, 722. doi:10.1038/nnano.2010.172 |

| 45. | Nagashio, K.; Yamashita, T.; Nishimura, T.; Kita, K.; Toriumi, A. J. Appl. Phys. 2011, 110, 024513. doi:10.1063/1.3611394 |

| 45. | Nagashio, K.; Yamashita, T.; Nishimura, T.; Kita, K.; Toriumi, A. J. Appl. Phys. 2011, 110, 024513. doi:10.1063/1.3611394 |

| 50. | Sagade, A. A.; Neumaier, D.; Schall, D.; Otto, M.; Pesquera, A.; Centeno, A.; Elorza, A. Z.; Kurz, H. Nanoscale 2015, 7, 3558. doi:10.1039/C4NR07457B |

| 50. | Sagade, A. A.; Neumaier, D.; Schall, D.; Otto, M.; Pesquera, A.; Centeno, A.; Elorza, A. Z.; Kurz, H. Nanoscale 2015, 7, 3558. doi:10.1039/C4NR07457B |

| 33. | Pasternak, I.; Wesolowski, M.; Jozwik, I.; Lukosius, M.; Lupina, G.; Dabrowski, P.; Baranowski, J. M.; Strupinski, W. Sci. Rep. 2016, 6, 21773. doi:10.1038/srep21773 |

| 4. | Banszerus, L.; Schmitz, M.; Engels, S.; Dauber, J.; Oellers, M.; Haupt, F.; Watanabe, K.; Taniguchi, T.; Beschoten, B.; Stampfer, C. Sci. Adv. 2015, 1, e1500222. doi:10.1126/sciadv.1500222 |

| 45. | Nagashio, K.; Yamashita, T.; Nishimura, T.; Kita, K.; Toriumi, A. J. Appl. Phys. 2011, 110, 024513. doi:10.1063/1.3611394 |

| 49. | Neumann, C.; Reichardt, S.; Venezuela, P.; Drögeler, M.; Banszerus, L.; Schmitz, M.; Watanabe, K.; Taniguchi, T.; Mauri, F.; Beschoten, B.; Rotkin, S. V.; Stampfer, C. Nat. Commun. 2015, 6, 8429. doi:10.1038/ncomms9429 |

| 46. | Caridad, J. M.; Rossella, F.; Bellani, V.; Maicas, M.; Patrini, M.; Díez, E. J. Appl. Phys. 2010, 108, 084321. doi:10.1063/1.3500295 |

| 47. | Ahn, G.; Kim, H. R.; Ko, T. Y.; Choi, K.; Watanabe, K.; Taniguchi, T.; Hong, B. H.; Ryu, S. ACS Nano 2013, 7, 1533. doi:10.1021/nn305306n |

| 48. | Lafkioti, M.; Krauss, B.; Lohmann, T.; Zschieschang, U.; Klauk, H.; v. Klitzing, K.; Smet, J. H. Nano Lett. 2010, 10, 1149. doi:10.1021/nl903162a |

| 51. | Aria, A. I.; Nakanishi, K.; Xiao, L.; Braeuninger-Weimer, P.; Sagade, A. A.; Alexander-Webber, J. A.; Hofmann, S. ACS Appl. Mater. Interfaces 2016, 8, 30564. doi:10.1021/acsami.6b09596 |

| 52. | Politou, M.; Asselberghs, I.; Radu, I.; Conard, T.; Richard, O.; Lee, C. S.; Martens, K.; Sayan, S.; Huyghebaert, C.; Tokei, Z.; De Gendt, S.; Heyns, M. Appl. Phys. Lett. 2015, 107, 153104. doi:10.1063/1.4933192 |

| 50. | Sagade, A. A.; Neumaier, D.; Schall, D.; Otto, M.; Pesquera, A.; Centeno, A.; Elorza, A. Z.; Kurz, H. Nanoscale 2015, 7, 3558. doi:10.1039/C4NR07457B |

| 1. | Novoselov, K. S.; Geim, A. K.; Morozov, S. V.; Jiang, D.; Zhang, Y.; Dubonos, S. V.; Grigorieva, I. V.; Firsov, A. A. Science 2004, 306, 666. doi:10.1126/science.1102896 |

| 5. | Novoselov, K. S.; Fal'ko, V. I.; Colombo, L.; Gellert, P. R.; Schwab, M. G.; Kim, K. Nature 2012, 490, 192. doi:10.1038/nature11458 |

| 20. | de la Rosa, C. J. L.; Lindvall, N.; Cole, M. T.; Nam, Y.; Löffler, M.; Olsson, E.; Yurgens, A. Appl. Phys. Lett. 2013, 102, 22101. doi:10.1063/1.4775583 |

| 21. | Gao, L.; Ren, W.; Xu, H.; Jin, L.; Wang, Z.; Ma, T.; Ma, L.-P.; Zhang, Z.; Fu, Q.; Peng, L.-M.; Bao, X.; Cheng, H.-M. Nat. Commun. 2012, 3, 699. doi:10.1038/ncomms1702 |

| 58. | Wang, L.; Meric, I.; Huang, P. Y.; Gao, Q.; Gao, Y.; Tran, H.; Taniguchi, T.; Watanabe, K.; Campos, L. M.; Muller, D. A.; Guo, J.; Kim, P.; Hone, J.; Shepard, K. L.; Dean, C. R. Science 2013, 342, 614. doi:10.1126/science.1244358 |

| 4. | Banszerus, L.; Schmitz, M.; Engels, S.; Dauber, J.; Oellers, M.; Haupt, F.; Watanabe, K.; Taniguchi, T.; Beschoten, B.; Stampfer, C. Sci. Adv. 2015, 1, e1500222. doi:10.1126/sciadv.1500222 |

| 19. | Suk, J. W.; Kitt, A.; Magnuson, C. W.; Hao, Y.; Ahmed, S.; An, J.; Swan, A. K.; Goldberg, B. B.; Ruoff, R. S. ACS Nano 2011, 5, 6916. doi:10.1021/nn201207c |

| 3. | Bolotin, K. I.; Sikes, K. J.; Jiang, Z.; Klima, M.; Fudenberg, G.; Hone, J.; Kim, P.; Stormer, H. L. Solid State Commun. 2008, 146, 351. doi:10.1016/j.ssc.2008.02.024 |

| 19. | Suk, J. W.; Kitt, A.; Magnuson, C. W.; Hao, Y.; Ahmed, S.; An, J.; Swan, A. K.; Goldberg, B. B.; Ruoff, R. S. ACS Nano 2011, 5, 6916. doi:10.1021/nn201207c |

| 57. | Chaves, F. A.; Jiménez, D.; Sagade, A. A.; Kim, W.; Riikonen, J.; Lipsanen, H.; Neumaier, D. 2D Mater. 2015, 2, 025006. doi:10.1088/2053-1583/2/2/025006 |

| 2. | Ferrari, A. C.; Bonaccorso, F.; Fal’ko, V.; Novoselov, K. S.; Roche, S.; Bøggild, P.; Borini, S.; Koppens, F. H. L.; Palermo, V.; Pugno, N.; Garrido, J. A.; Sordan, R.; Bianco, A.; Ballerini, L.; Prato, M.; Lidorikis, E.; Kivioja, J.; Marinelli, C.; Ryhänen, T.; Morpurgo, A.; Coleman, J. N.; Nicolosi, V.; Colombo, L.; Fert, A.; Garcia-Hernandez, M.; Bachtold, A.; Schneider, G. F.; Guinea, F.; Dekker, C.; Barbone, M.; Sun, Z.; Galiotis, C.; Grigorenko, A. N.; Konstantatos, G.; Kis, A.; Katsnelson, M.; Vandersypen, L.; Loiseau, A.; Morandi, V.; Neumaier, D.; Treossi, E.; Pellegrini, V.; Polini, M.; Tredicucci, A.; Williams, G. M.; Hong, B. H.; Ahn, J.-H.; Kim, J. M.; Zirath, H.; van Wees, B. J.; van der Zant, H.; Occhipinti, L.; Di Matteo, A.; Kinloch, I. A.; Seyller, T.; Quesnel, E.; Feng, X.; Teo, K.; Rupesinghe, N.; Hakonen, P.; Neil, S. R. T.; Tannock, Q.; Löfwander, T.; Kinaret, J. Nanoscale 2015, 7, 4598. doi:10.1039/C4NR01600A |

| 19. | Suk, J. W.; Kitt, A.; Magnuson, C. W.; Hao, Y.; Ahmed, S.; An, J.; Swan, A. K.; Goldberg, B. B.; Ruoff, R. S. ACS Nano 2011, 5, 6916. doi:10.1021/nn201207c |

| 58. | Wang, L.; Meric, I.; Huang, P. Y.; Gao, Q.; Gao, Y.; Tran, H.; Taniguchi, T.; Watanabe, K.; Campos, L. M.; Muller, D. A.; Guo, J.; Kim, P.; Hone, J.; Shepard, K. L.; Dean, C. R. Science 2013, 342, 614. doi:10.1126/science.1244358 |

| 59. | Leong, W. S.; Gong, H.; Thong, J. T. L. ACS Nano 2014, 8, 994. doi:10.1021/nn405834b |

| 10. | König, M.; Ruhl, G.; Batke, J.-M.; Lemme, M. C. Nanoscale 2016, 8, 15490. doi:10.1039/C6NR03954E |

| 13. | CRC Handbook of Chemistry and Physics, 92nd Edition. https://www.crcpress.com/CRC-Handbook-of-Chemistry-and-Physics-92nd-Edition/Haynes/p/book/9781439855126 (accessed Jan 18, 2017). |

| 54. | Liu, W.; Wei, J.; Sun, X.; Yu, H. Crystals 2013, 3, 257. doi:10.3390/cryst3010257 |

| 8. | Kim, K. S.; Zhao, Y.; Jang, H.; Lee, S. Y.; Kim, J. M.; Kim, K. S.; Ahn, J.-H.; Kim, P.; Choi, J.-Y.; Hong, B. H. Nature 2009, 457, 706. doi:10.1038/nature07719 |

| 9. | Bae, S.; Kim, H.; Lee, Y.; Xu, X.; Park, J.-S.; Zheng, Y.; Balakrishnan, J.; Lei, T.; Ri Kim, H.; Song, Y. I.; Kim, Y.-J.; Kim, K. S.; Özyilmaz, B.; Ahn, J.-H.; Hong, B. H.; Iijima, S. Nat. Nanotechnol. 2010, 5, 574. doi:10.1038/nnano.2010.132 |

| 14. | Lee, C. S.; Baraton, L.; He, Z.; Maurice, J.-L.; Chaigneau, M.; Pribat, D.; Cojocaru, C. S. Proc. SPIE 2010, 7761, 77610P. doi:10.1117/12.861866 |

| 15. | Terasawa, T.; Saiki, K. Carbon 2012, 50, 869. doi:10.1016/j.carbon.2011.09.047 |

| 16. | Li, Z.; Wu, P.; Wang, C.; Fan, X.; Zhang, W.; Zhai, X.; Zeng, C.; Li, Z.; Yang, J.; Hou, J. ACS Nano 2011, 5, 3385. doi:10.1021/nn200854p |

| 17. | Zhang, B.; Lee, W. H.; Piner, R.; Kholmanov, I.; Wu, Y.; Li, H.; Ji, H.; Ruoff, R. S. ACS Nano 2012, 6, 2471. doi:10.1021/nn204827h |

| 18. | Jiang, L.; Niu, T.; Lu, X.; Dong, H.; Chen, W.; Liu, Y.; Hu, W.; Zhu, D. J. Am. Chem. Soc. 2013, 135, 9050. doi:10.1021/ja4031825 |

| 55. | Wilmart, Q.; Inhofer, A.; Boukhicha, M.; Yang, W.; Rosticher, M.; Morfin, P.; Garroum, N.; Fève, G.; Berroir, J.-M.; Plaçais, B. Sci. Rep. 2016, 6, 21085. doi:10.1038/srep21085 |

| 56. | Cusati, T.; Fiori, G.; Gahoi, A.; Passi, V.; Fortunelli, A.; Lemme, M.; Iannaccone, G. Understanding the nature of metal-graphene contacts: A theoretical and experimental study. In Electron Devices Meeting (IEDM), 2015 IEEE International, Washington, DC, USA, Dec 7–9, 2015; IEEE, 2016; 12.7.1–12.7.4. doi:10.1109/IEDM.2015.7409686 |

| 7. | Kang, J.; Shin, D.; Bae, S.; Hong, B. H. Nanoscale 2012, 4, 5527. doi:10.1039/c2nr31317k |

| 52. | Politou, M.; Asselberghs, I.; Radu, I.; Conard, T.; Richard, O.; Lee, C. S.; Martens, K.; Sayan, S.; Huyghebaert, C.; Tokei, Z.; De Gendt, S.; Heyns, M. Appl. Phys. Lett. 2015, 107, 153104. doi:10.1063/1.4933192 |

| 4. | Banszerus, L.; Schmitz, M.; Engels, S.; Dauber, J.; Oellers, M.; Haupt, F.; Watanabe, K.; Taniguchi, T.; Beschoten, B.; Stampfer, C. Sci. Adv. 2015, 1, e1500222. doi:10.1126/sciadv.1500222 |

| 6. | Li, X.; Colombo, L.; Ruoff, R. S. Adv. Mater. 2016, 28, 6247. doi:10.1002/adma.201504760 |

| 11. | Jiang, J.-W.; Wang, J.-S.; Li, B. Phys. Rev. B 2009, 80, 205429. doi:10.1103/PhysRevB.80.205429 |

| 12. | Yoon, D.; Son, Y.-W.; Cheong, H. Nano Lett. 2011, 11, 3227. doi:10.1021/nl201488g |

| 53. | Gahoi, A.; Wagner, S.; Bablich, A.; Kataria, S.; Passi, V.; Lemme, M. C. Solid-State Electron. 2016, 125, 234. doi:10.1016/j.sse.2016.07.008 |

| 23. | Temmen, M.; Ochedowski, O.; Schleberger, M.; Reichling, M.; Bollmann, T. R. J. New J. Phys. 2014, 16, 053039. doi:10.1088/1367-2630/16/5/053039 |

| 19. | Suk, J. W.; Kitt, A.; Magnuson, C. W.; Hao, Y.; Ahmed, S.; An, J.; Swan, A. K.; Goldberg, B. B.; Ruoff, R. S. ACS Nano 2011, 5, 6916. doi:10.1021/nn201207c |

| 22. | Koenig, S. P.; Boddeti, N. G.; Dunn, M. L.; Bunch, J. S. Nat. Nanotechnol. 2011, 6, 543. doi:10.1038/nnano.2011.123 |

| 60. | Han, S.-J.; Garcia, A. V.; Oida, S.; Jenkins, K. A.; Haensch, W. Nat. Commun. 2014, 5, 3086. doi:10.1038/ncomms4086 |

| 28. | Kim, J.; Lee, G.; Kim, J. Appl. Phys. Lett. 2015, 107, 033104. doi:10.1063/1.4926605 |

| 26. | Ismach, A.; Druzgalski, C.; Penwell, S.; Schwartzberg, A.; Zheng, M.; Javey, A.; Bokor, J.; Zhang, Y. Nano Lett. 2010, 10, 1542. doi:10.1021/nl9037714 |

| 27. | Banno, K.; Mizuno, M.; Fujita, K.; Kubo, T.; Miyoshi, M.; Egawa, T.; Soga, T. Appl. Phys. Lett. 2013, 103, 082112. doi:10.1063/1.4818342 |

| 24. | Liang, X.; Sperling, B. A.; Calizo, I.; Cheng, G.; Hacker, C. A.; Zhang, Q.; Obeng, Y.; Yan, K.; Peng, H.; Li, Q.; Zhu, X.; Yuan, H.; Hight Walker, A. R.; Liu, Z.; Peng, L.; Richter, C. A. ACS Nano 2011, 5, 9144. doi:10.1021/nn203377t |

| 25. | Gao, L.; Ni, G.-X.; Liu, Y.; Liu, B.; Castro Neto, A. H.; Loh, K. P. Nature 2014, 505, 190. doi:10.1038/nature12763 |

© 2017 Ruhl et al.; licensee Beilstein-Institut.

This is an Open Access article under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/4.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

The license is subject to the Beilstein Journal of Nanotechnology terms and conditions: (http://www.beilstein-journals.org/bjnano)