Abstract

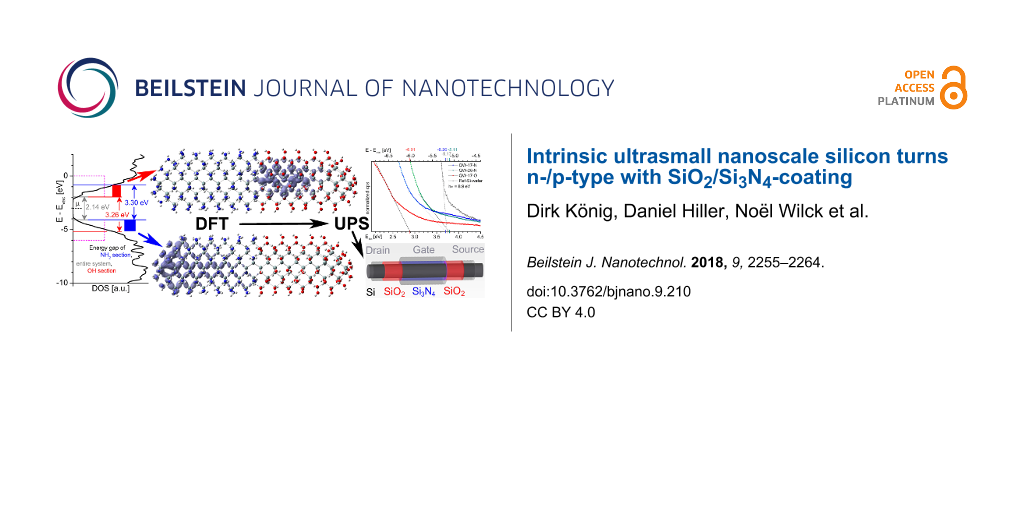

Impurity doping of ultrasmall nanoscale (usn) silicon (Si) currently used in ultralarge scale integration (ULSI) faces serious miniaturization challenges below the 14 nm technology node such as dopant out-diffusion and inactivation by clustering in Si-based field-effect transistors (FETs). Moreover, self-purification and massively increased ionization energy cause doping to fail for Si nano-crystals (NCs) showing quantum confinement. To introduce electron- (n-) or hole- (p-) type conductivity, usn-Si may not require doping, but an energy shift of electronic states with respect to the vacuum energy between different regions of usn-Si. We show in theory and experiment that usn-Si can experience a considerable energy offset of electronic states by embedding it in silicon dioxide (SiO2) or silicon nitride (Si3N4), whereby a few monolayers (MLs) of SiO2 or Si3N4 are enough to achieve these offsets. Our findings present an alternative to conventional impurity doping for ULSI, provide new opportunities for ultralow power electronics and open a whole new vista on the introduction of p- and n-type conductivity into usn-Si.

Introduction

Impurity doping of silicon (Si) has been a key technique and prerequisite for Si-based electronics for decades [1]. Miniaturization in Si ultralarge scale integration (ULSI) became increasingly difficult as device features approached the characteristic lengths of dopant out-diffusion, clustering and inactivation [2]. The considerable broadening of dopant profiles from drain/source regions into gate areas persists [3]. Moreover, required ULSI transistor functionality and emerging applications of Si-nanocrystals (NCs) [4] unveiled additional doping issues: self-purification [5,6], suppressed dopant ionization [7,8] and dopant-associated defect states [8,9].

Modulation doping – i.e., doping of materials adjacent to semiconductors which then provide free carriers to the unperturbed semiconductor – was first used for group III–V semiconductor combinations such as GaAs/AlAs in the late 1970s [10]. Recently, Si modulation doping of adjacent dielectric layers based on nitrides [11] and oxides [12], in analogy to modulation doping of III–V semiconductors, were shown to be an alternative to conventional impurity doping.

It would be ideal to achieve electron- (n-) or hole- (p-) type conductivity in usn-Si without doping, thereby avoiding all dopant-related issues mentioned above. Such conductivity can be induced by an energy offset (ΔE) of the same electronic states (lowest unoccupied molecular orbital (LUMO) or highest occupied molecular orbital (HOMO)) between different regions of the same usn-Si system [13,14]. This concept eliminates doping altogether, leading to a lower inelastic carrier scattering rate and higher carrier mobility which allow for decreased heat loss and bias voltages in ULSI. Such properties enable Si-FET technology to work at even smaller structure sizes, potentially enabling Moore’s law to reach the Si-crystallization limit of ca. 1.5 nm [15].

In our present work, we prove by hybrid-density functional theory (h-DFT) simulations and synchrotron-based long-term ultraviolet photoelectron spectroscopy (UPS) that usn-Si indeed can have a massive ΔE of their electronic density of states (DOS) when embedded in SiO2 or Si3N4. We use further h-DFT results of a Si-nanowire (NWire) covered in SiO2 and Si3N4 to examine the device behaviour of an undoped Si-NWire FET based solely on CMOS-compatible materials (e.g., Si, SiO2, Si3N4) using the nonequilibrium Green’s function (NEGF) approach.

Following an explanation of the theoretical and experimental methods used, we turn to results for Si-NCs obtained from h-DFT. Here, we focus on the electronic structure of Si-NCs as a function of the embedding dielectric and its thickness of up to 3 monolayers (MLs). The latter dependence requires the use of NCs to keep the h-DFT computation effort practicable; NWires with more than 1 ML dielectric embedding are beyond the feasible computation effort at the level of accuracy we use. As an ultimate theoretical test, we present h-DFT results of two Si-NCs, one embedded in SiO2 and the other embedded in Si3N4, presenting the entire system under investigation within one approximant. An interface charge transfer (ICT) of electrons from the usn-Si volume to the anions of the embedding dielectric – nitrogen (N) or oxygen (O) – is at the core of the energy shift [14]. We explain the shift of usn-Si electronic states towards the vacuum level Evac when embedded in Si3N4 and further below Evac when embedded in SiO2 by the quantum chemistry of N and O with respect to Si. The next section contains experimental results, namely the thickness determination of embedded Si nanowells (NWells) by transmission electron microscopy (TEM) and the measurement of the highest occupied DOS over energy for Si-NWell samples embedded in SiO2 or Si3N4 by synchrotron-based long-term UPS. With this experimental confirmation of our h-DFT results, we present the concept of undoped Si-NWire field-effect transistors (FETs). We show further h-DFT results of a Si-NWire of 5.2 nm length and 1.4 nm diameter, terminated to 50% with 1 ML of Si3N4 (NH2 groups) and to 50% with 1 ML of SiO2 (OH groups). These h-DFT results deliver key input data to NEGF device simulations as a proof-of-concept for the undoped Si-NWire FET. A wealth of information on h-DFT accuracy as compared to experiment, details of UPS measurements and NEGF are contained in Supporting Information File 1.

Experimental

h-DFT material calculations

Hybrid-DFT calculations were carried out in real space with a molecular orbital basis set (MO-BS) and both Hartree–Fock (HF) and h-DFT methods as described below, employing the Gaussian03 and Gaussian09 program packages [16,17]. Initially, the MO-BS wavefunction ensemble was tested and optimized for stability with respect to describing the energy minimum of the approximant (variational principle; stable = opt) with the HF method using a Gaussian-type 3-21G MO-BS [18] (HF/3-21G). This MO wavefunction ensemble was then used for the structural optimisation of the approximant to arrive at its most stable configuration (maximum integral over all bond energies), again following the HF/3-21G route. Using these optimized geometries, their electronic structure was calculated again by testing and optimizing the MO-BS wavefunction ensemble with the B3LYP hybrid DF [19,20] and the Gaussian-type 6-31G(d) MO-BS which contains d-polarization functions (B3LYP/6-31G(d)) [21] to describe the strong polar nature of atomic bonds of Si to O and N. The root mean square (RMS) and peak force convergence limits for all atoms were 3 × 10−4 Ha/a0 (Hartrees per Bohr radius) or 80 meV/nm and 4.5 × 10−4 Ha/a0 or 120 meV/nm, respectively. Tight convergence criteria were applied to the self-consistent field routine. Ultrafine integration grids were used throughout. During all calculations, no symmetry constraints were applied to MOs. An extensive accuracy evaluation can be found in the Supporting Information File 1 of this article and elsewhere [13,14,22]. The approximants and MOs were visualized with GaussView 5 [23]. The electronic DOS were calculated from MO eigenenergies, applying a Gaussian broadening of 0.2 eV.

Sample preparation

Samples comprising a Si3N4-embedded NWell were fabricated by plasma-enhanced chemical vapour deposition (PECVD) using SiH4+NH3+N2 for Si3N4 and SiH4+Ar for amorphous Si [24]. As substrates, n-type Si wafers (Sb doping, 5 to 15 × 10−3 Ω cm) of (111)-surface orientation underwent wet-chemical cleaning. After deposition the wafers were annealed in a quartz tube furnace for 1 min at 1100 °C in pure N2 ambient to induce Si crystallization. Subsequently, the samples were H2-passivated at 450 °C for 1 h. A 4.5 nm thick Si3N4 spacer layer served to suppress excited electrons from the Si wafer to interfere with electrons from the Si-NWell during UPS.

Samples comprising a SiO2-embedded NWell were processed by etching the top c-Si layer of an Si-on-insulator (SOI) wafer with 200 nm buried SiO2 (BOX) down to ca. 3 nm. The subsequent oxidation resulted in a 1.7 nm Si-NWell and 1.5 nm SiO2 capping.

Si reference samples were processed by etching a 5 to 15 × 10−3 Ω cm Sb-doped n-type (111)-Si wafer in buffered hydrofluoric acid, and the sample was immediately mounted under a N2-shower then swiftly loaded into the ultrahigh vacuum (UHV) annealing chamber.

All NWell samples were contacted via a lateral metal contact frame on the front surface which was processed by photolithographical structuring, wet-chemical mesa etching and thermal evaporation of Al. The reference Si-wafer was contacted directly on its front surface.

Characterization

UPS measurements were carried out at the BaDElPh beamline [25] at the Elettra Synchrotron in Trieste, Italy, in top-up mode (310 mA electron ring current). All samples were subject to a UHV anneal for 90 min at 500 K to desorb water and air-related species from the sample surface prior to the measurements. Single scans of spectra were recorded over 12 h per NWell sample and subsequently added up for eliminating white noise. Scans for the Si-reference sample were recorded over 2 h and subsequently added up. All NWell samples were exited with a photon energy of 8.9 eV and a photon flux of 2 × 1012 s−1. The incident angle of the UV beam onto the sample was 50° with respect to the sample surface normal, and excited electrons were collected with an electron analyzer along the normal vector of the sample surface. The energy calibration of the UPS was realized using a tantalum (Ta) stripe in electrical contact to the sample as a work function reference. Further UPS-data of SiO2 and Si3N4 reference samples as well as UPS signal normalization are available in Supporting Information File 1.

All samples for TEM investigation were capped with a protective SiO2-layer to facilitate the preparation of cross sections by the focused ion beam technique using a FEI Strata FIB 205 workstation. Some samples were further thinned by means of a Fischione NanoMill. The TEM analysis of the cross sections was performed on a FEI Tecnai F20 TEM operated at 200 kV at the Central Facility for Electron Microscopy, RWTH Aachen University, and on the spherical aberration corrected FEI Titan 80-300 TEM operated at 300 kV at Ernst Ruska-Centre, Forschungszentrum Jülich [26].

In addition, the Si-NWell thickness was measured by ellipsometry. The thickness of the Si-NWells in Si3N4 (in SiO2) were measured using a Woollam M-2000 ellipsometer (ACCURION nanofilm ep4se ellipsometer). All thickness measurements confirmed the values obtained from TEM.

NEGF device simulations

A homemade NEGF simulation program was used for simulating nanoscale device characteristics based on h-DFT results of Si-NWires. The simulations are based on a self-consistent solution of the Poisson and Schrödinger equations on a finite difference grid. A one-dimensional, modified Poisson equation is considered here that provides an adequate description of the electrostatics of wrap-gate nanowire transistors [27]. Buettiker probes, i.e., virtual contacts, are attached to each finite difference site in order to mimic inelastic scattering [28]. To this end, an additional self-consistent calculation of the quasi-Fermi level throughout the device is computed, ensuring that the net current flow into/out of each Buettiker probe is zero. The electrostatics within the gate underlap region has been taken into consideration with a conformal mapping technique that maps the underlap region to a parallel-plate capacitor and allows the extraction of a space-dependent effective oxide thickness that is used in this region. The “doping” due to the presence of the SiO2 coating is taken into consideration as a volume, active dopant concentration (see Supporting Information File 1); the presence of the Si3N4 layer underneath the gate is accounted for by an appropriate shift of the threshold voltage of the transistor (see Supporting Information File 1).

Results and Discussion

h-DFT calculations of embedded Si nanocrystals, fundamentals of energy offset

For evaluating the energy shift ΔE of the electronic DOS between usn-Si covered with SiO2 or Si3N4, we calculated two Si-NCs (Si10, 0.8 nm size) within one approximant; one NC is embedded in SiO2 and one NC resides in Si3N4 (Figure 1). We found earlier that – regarding DFT – Si10-NCs are the smallest NCs above the atomic limit below which Si-clusters behave as small molecules in the gas phase [13]. The frontier-OMOs exist within the Si3N4-embedded Si-NC (Figure 1, inset iii), while the frontier-UMO exists within the SiO2-embedded Si-NC (Figure 1, inset ii), with ΔE of the occupied frontier MOs of 0.5 eV and of 1 eV for the unoccupied frontier MOs between both NCs. These ΔE values are smaller when compared to individual embedded NCs (see Figure 2c and Supporting Information File 1) due to the inter-NC distance of merely 1 nm, accounting for some ICT convergence from Si NCs to SiO2 or Si3N4. From Figure 2c we see that an ICT saturation is evident for ≥2 ML SiO2. This saturation is less apparent when Si3N4 is applied as the embedding matrix. We explain this behaviour together with the ΔE by the quantum-chemical properties of Si, N and O.

![[2190-4286-9-210-1]](/bjnano/content/figures/2190-4286-9-210-1.jpg?scale=2.0&max-width=1024&background=FFFFFF)

Figure 1: Energy offsets with SiO2- and Si3N4-embedding for one Si10-NC (0.8 nm size) embedded in SiO2 and the other Si10-NC embedded in Si3N4 within one approximant. The main graph shows the electronic DOS. MOs localized in Si3N4- (SiO2-) embedded Si-NC are shown in blue (red); the reduced length of the MOs corresponds to partial localization in Si10-NC, with the remainder of the MO being localized within the dielectric. The chemical potential of the entire approximant μ is shown as a dashed-dotted line. Graphs (i) to (iv) show iso-density plots (1 × 10−3 states/a03 = 6.76 states/nm3) of frontier MOs marked by (i) to (iv) in the DOS plot. Si10-NCs are shown in cyan, Si in SiO2 and Si3N4 in grey, O in red, N in blue and H in white.

Figure 1: Energy offsets with SiO2- and Si3N4-embedding for one Si10-NC (0.8 nm size) embedded in SiO2 and th...

![[2190-4286-9-210-2]](/bjnano/content/figures/2190-4286-9-210-2.jpg?scale=2.0&max-width=1024&background=FFFFFF)

Figure 2: Evolution of energy offsets for SiO2- and Si3N4-embedded Si10-NCs (0.8 nm size) as a function of embedding SiO2- or Si3N4-thickness: (a) Si10-NC embedded in 3 ML Si3N4 after structural optimization. (b) Si10-NC embedded in 3 ML SiO2 after structural optimization. For atoms colors see Figure 1. (c) Evolution of HOMO and LUMO energies relative to vacuum energy Evac (left scale) and total Si10-NC ionization (right scale) with increasing thickness of embedding dielectric. For SiO2-embedding, the ICT and the associated shift in HOMO and LUMO energies away from Evac saturate quickly. For Si3N4-embedding, the HOMO energy shifts towards Evac. The LUMO energy shift varies around a constant value as shown by a linear fit to LUMO energies (cyan line) as a function of Si3N4 thickness. The positive NC ionization remains nearly unchanged. These features are due to the positive electron affinity X and the anionic nature of N, resulting in electron delocalization from the NC (ionization) without strong electron localization at N as is the case for O.

Figure 2: Evolution of energy offsets for SiO2- and Si3N4-embedded Si10-NCs (0.8 nm size) as a function of em...

Both anions, N and O, dominate electronic bonds to Si by delocalizing a substantial partition of Si valence electrons to form strong polar bonds [13], giving rise to ICT from usn-Si into the respective dielectric (SiO2, Si3N4) [14]. A high ionicity of bond (IOB) and strong negative electron affinity (X) of O result in a strong localization of Si-NC valence electrons. This localization corresponds to increased binding energies – the ICT shifts all MOs away from Evac. N is the only anionic element with a positive X [29] which is key for ΔE together with the smaller IOB of N to Si. Unlike O, the valence electrons delocalized from Si-NCs are not strongly localized at N due to its positive X and lower IOB to Si. Such delocalized MOs correspond to states with substantially lowered binding energy, yielding to a shift of MOs towards Evac. Accordingly, frontier-MOs of the Si3N4-embedded NC (Figure 1, insets i and iii) show stronger delocalization as compared to frontier-MOs of the SiO2-embedded Si-NC (Figure 1, inset ii and iv).

Table 1 summarizes the specific properties of Si, O and N relevant to the nature of ICT. The larger bond length of Si–N as compared to Si–O arguably contributes to electron delocalization, while the lower packing fraction of SiO2 is irrelevant in this respect due to strong electron localization at O. Both anions possess about the same ionization due to their IOB to Si together with N and O being trivalent and divalent, respectively. This finding is supported by the virtually identical NC ionization energy of fully NH2- vs OH-terminated Si-NCs (see Supporting Information File 1).

Table 1: Fundamental properties of N, O and Si: Ionization energy (Eion), electron affinity (X), electronegativity (EN), ensuing ionicity of bond (IOB) to Si and experimental values of characteristic bond lengths [29]. See also to Supporting Information File 1 for the latter.

| element | Eiona [eV] | X [eV] | ENb | IOB to Si [%] | dbond to Si [nm] |

| N | 14.53 | +0.07 | 3.07 | 36 | 0.1743 (Si3N4) |

| O | 13.36 | −1.46 | 3.50 | 54 | 0.1626 (SiO2) |

| Si | 8.15 | −2.08 | 1.74 | 0 | 0.2387 (bulk Si)c |

aRefers to first valence electron.

bValues after Allred and Rochow.

cWith unit cell length of 0.5431 nm [30].

As will be shown experimentally in the next section, the resulting ΔE of the frontier-MOs induces an n-type (p-type) behaviour in usn-Si by SiO2-embedding (Si3N4-embedding). For the ICT, and thus the intensity of p- or n-type behaviour, the ratio of interface bonds to atoms forming the Si-NWell, -NWire or -NC is an important parameter [31]. It describes the amount of entities (Si atoms) to be ionized over a certain amount of transfer paths (interface bonds) and depends on the interface facet orientation of the usn-Si volume as well as on its surface-to-volume ratio.

Sample characterization: TEM and synchrotron-based long-term UPS

We experimentally verified our theoretical findings by characterizing samples comprising 1.7 nm and 2.6 nm thick Si-NWells embedded in SiO2 or Si3N4 together with a Si reference sample (Figure 3a–d) using synchrotron UPS.

![[2190-4286-9-210-3]](/bjnano/content/figures/2190-4286-9-210-3.png?scale=2.0&max-width=1024&background=FFFFFF)

Figure 3: Structures of samples investigated by synchrotron UPS: (a) Si-reference, (b) 1.7 nm Si-NWell in Si3N4, (c) 1.7 nm Si-NWell in SiO2, (d) 2.6 nm Si-NWell in Si3N4. Sample codes are shown on top of each structure.

Figure 3: Structures of samples investigated by synchrotron UPS: (a) Si-reference, (b) 1.7 nm Si-NWell in Si3N...

Figure 4a–c shows high-resolution cross-section TEM images of each NWell sample. Such ultrathin Si layers require long signal acquisition times in UPS due to the short mean free path of valence electrons excited above Evac[32] in compound with the small Si-volume probed. This is in particular true for Si-NWells embedded in Si3N4 as discussed in Supporting Information File 1.

![[2190-4286-9-210-4]](/bjnano/content/figures/2190-4286-9-210-4.jpg?scale=2.0&max-width=1024&background=FFFFFF)

Figure 4: Cross-section HR-TEM images of samples QW-17-N (a), QW-17-O (b) and QW-26-N (c). Semi-transparent strips show layer thicknesses of Si3N4 (cyan), Si-NWells (magenta) and SiO2 (orange).

Figure 4: Cross-section HR-TEM images of samples QW-17-N (a), QW-17-O (b) and QW-26-N (c). Semi-transparent s...

UPS spectra are shown in Figure 5. The reference sample (Si-ref) yielded a valence band edge at the ionization energy Eion = Evac − 5.17 eV as known for bulk Si [33]. We obtained Eion = Evac − 6.01 eV for the 1.7 nm Si-NWell in SiO2 and Eion = Evac − 5.20 eV (Evac − 5.11 eV) for the 1.7 (2.6) nm Si-NWell in Si3N4. The difference in ionization energy ΔEion between 1.7 nm Si-NWells in SiO2 and Si3N4 is 0.81 eV which clearly confirms our h-DFT calculations. For the 2.6 nm NWell embedded in Si3N4 we obtain a Eion of 0.06 eV below the value of bulk Si (Figure 5b). The ICT may thus overcompensate quantum confinement and induce a negative ΔEion to bulk Si. The ICT impact length on Si-NWells can be related to Si-NWires and Si-NCs to scale 1/2/3 for NWells/NWires/NCs [14]. This relation explains why larger ΔE values for HOMOs and LUMOs are obtained for Si-NWires (Figure 6) as compared to Si-NWells (Figure 5b).

![[2190-4286-9-210-5]](/bjnano/content/figures/2190-4286-9-210-5.png?scale=2.0&max-width=1024&background=FFFFFF)

Figure 5: Experimental evidence of HOMO ΔE by synchrotron UPS: (a) scans of NWell samples and a hydrogen-terminated (111) Si wafer as a reference for the Si-NWells. The valence band edges of Si-NWells detected are located within the magenta lines and shown in (b). The bottom energy scales refer to electron kinetic energy up to UV photon energy. The top energy scale shows the energetic position of electrons relative to vacuum level with valence band edges and respective energy values as extracted from the spectra (dashed lines). The light green and cyan lines show the background fit of the amorphous Si3N4-matrix. The lower signal-to-noise ratio for Si-NWells embedded in Si3N4 as compared to SiO2 is comprehensively evaluated and discussed in Supporting Information File 1.

Figure 5: Experimental evidence of HOMO ΔE by synchrotron UPS: (a) scans of NWell samples and a hydrogen-term...

Concept of undoped Si nanowire FETs

With the ΔE values of the usn-Si coated with SiO2 vs Si3N4 confirmed by synchrotron UPS, we now turn to its application to undoped ULSI Si devices.

NWire-FETs are a cornerstone of future ULSI technology development due to their excellent controllability by wrap-around gate architecture [34,35]. However, the ultrasmall NWire diameter required to guarantee the electrostatic integrity of the devices causes conventional doping to fail. Metal–Si contacts formed by, e.g., silicide formation [36] result in rather high Schottky-barriers at the source/drain-channel interfaces that deteriorate the switching behaviour and on-state performance.

h-DFT calculations of Si nanowires relevant to devices

As we will show below, a Si-NWire with a combined SiO2-/Si3N4-coating can work as a highly scalable, high-performance and dopant-free metal-insulator-silicon (MIS) FET device. Using the same h-DFT methods as above, we computed the electronic properties of a Si233(NH2)87(OH)81 approximant manifesting a Si-NWire with 1.4 nm diameter and 5.2 nm length, whereby the two halves of this NWire are terminated with NH2 and OH groups, respectively. These functional groups correspond to 1 ML of the respective dielectric – NH2 groups to 1 ML Si3N4 and OH groups to 1 ML SiO2 (Figure 6).

![[2190-4286-9-210-6]](/bjnano/content/figures/2190-4286-9-210-6.jpg?scale=2.0&max-width=1024&background=FFFFFF)

Figure 6:

Electronic properties obtained by h-DFT for Si233(NH2)87(OH)81 NWire of 1.4 nm diameter and 5.2 nm length, terminated with NH2 on its left half emulating Si3N4-embedding and with OH on its right half emulating SiO2-embedding: (a) DOS over energy relative to vacuum level Evac. Red (blue) lines show HOMO–LUMO-gap of OH-terminated (NH2-terminated) NWire section. Global HOMO–LUMO gap shown in grey together with Fermi energy EF for entire NWire. Magenta DOS sections are enlarged to show MO locations for (b) frontier-OMOs and (c) frontier-UMOs along with ΔE for exclusive and dominant MO location in the respective NWire section. (d–g) Si233(NH2)87(OH)81 approximant after structural optimization; for atom colours see Figure 1. The approximant is shown with the sum of frontier-MO densities ρMO = as iso-density plots for: (d) frontier-OMOs exclusively located in the NH2-terminated NWire section (ρMO = 1 × 10−3 states/a03 = 6.76 states/nm3), (e) frontier-OMOs dominantly located in the NH2-terminated NWire section (ρMO = 3 × 10−3 states/a03 = 20.3 states/nm3). A slight distortion of atomic positions occurs at the OH-terminated end due to electrostatic forces, leading to a minor location of MOs otherwise exclusively residing in the NH2-terminated NWire section. This effect does not occur at NWire devices where SiO2 coverage is followed by a contact layer, see Figure 7. (f) Frontier-UMOs exclusively located in the OH-terminated NWire section (ρMO = 2 × 10−3 states/a03 = 13.5 states/nm3), and (g) frontier-UMOs dominantly located in the OH-terminated NWire section (ρMO = 3 × 10−3 states/a03 = 20.3 states/nm3). Values for ρMO are scaled to provide ρMO = 1 × 10−4 states/a03 = 0.675 states/nm3 per MO.

Figure 6: Electronic properties obtained by h-DFT for Si233(NH2)87(OH)81 NWire of 1.4 nm diameter and 5.2 nm ...

Figure 6a shows the DOS around the HOMO–LUMO gap. We determined the location of the densities of all frontier-MOs, ρMO = , within 2 eV from HOMO and LUMO. Frontier-OMOs are located within the NH2-terminated NWire section with a ΔE to corresponding MOs in the OH-terminated NWire section of ≈1.1 eV. Frontier-UMOs exist in the OH-terminated NWire section, whereby ΔE from the OH- to NH2-terminated NWire section is ≈1.2 eV. Again, the increased values of ΔE of respective frontier-MOs as compared to UPS results of Si-NWells confirm geometric effects [14].

Undoped Si-NWire FETs

The electronic structure of the Si233(NH2)87(OH)81 NWire allows ΔE values to be established for NWire electronic devices with a combined SiO2-/Si3N4-coating such as an undoped self-blocking p-channel FET (Figure 7).

![[2190-4286-9-210-7]](/bjnano/content/figures/2190-4286-9-210-7.jpg?scale=2.0&max-width=1024&background=FFFFFF)

Figure 7: Concept of an undoped FET consisting of a Si-NWire with drain/gate (channel)/source regions covered by ultrathin Si3N4/SiO2/Si3N4: (a) physical layout shown for self-blocking p-channel FET. Schematic band diagram of such an FET shown for (b) zero and (c) negative gate bias relative to source voltage, resulting in a conductive channel by shifting the electronic Si-NWire states pinned by SiO2. Interchanging Si3N4 and SiO2 layers yields self-blocking n-channel FETs and thereby CMOS-compatibility. This concept is applicable to other Si nanostructures with a high surface-to-volume ratio like fin-FETs.

Figure 7: Concept of an undoped FET consisting of a Si-NWire with drain/gate (channel)/source regions covered...

Using the ΔE value obtained from the Si233(NH2)87(OH)81 NWire approximant and above-described UPS results, we derive hole (p) and electron (n) densities. We obtain p = 5 × 1019 cm−3 (n ≈ 0 cm−3) for the Si3N4-coated NWire-regions (drain/source) and p = 71 cm−3 (n ≈ 0 cm−3) for the SiO2-coated NWire-regions (see Supporting Information File 1). These values will be used in the next section where results on NEGF device simulations are presented.

NEGF device simulations

NEGF simulations were realized considering a 1.7 nm thick undoped Si-NWire MISFET with a channel length of L = 5 nm in a wrap-gate architecture placed between two metallic contacts (Figure 8a). The channel is insulated by a SiO2 layer, yielding an effective oxide thickness of 2 nm. The source/drain and the gate electrode are insulated from each other by an underlap region of length lcon where the NWire is covered with a 2 nm thick Si3N4 (device I) or SiO2 (device II) layer, resulting in dopant concentration equivalents as mentioned above. Ni source/drain contacts are considered to yield effective Schottky-barriers of −0.05 eV for hole-injection into the Si-NWire valence band.

![[2190-4286-9-210-8]](/bjnano/content/figures/2190-4286-9-210-8.png?scale=2.0&max-width=1024&background=FFFFFF)

Figure 8: NEGF simulation results of undoped Si-NWire-FET illustrated in Figure 7: (a) gate-wrap-around Si-NWire FET showing parameters listed in graphs (b) and (c). (b) Valence band along the axis of device I (top, Si3N4-coated gate-underlap) and device II Si-NWire FET (bottom, entire Si-NWire SiO2-coated) in on-state-mode with VGS = −1.2 V. The centre schematic shows the NWire-FET device gate-position and gate-underlap. Schottky-potential barriers build up although the same Schottky-barrier-height at the metal–Si interface at drain and source were chosen in both devices to examine the effectiveness of “doping” (Si3N4-coating) of underlap areas. A shift of the Schottky-barrier for device II due to workfunction mismatch of Ni to the valence band of the SiO2-coated Si-NWire would lead to a further massive deterioration of the on-state performance of device II. (c) Transfer characteristics of device type I (black) and II (red) for VDS = 0.5 V, contact length lcon = 5 nm; the graph contains remaining parameters. The “doping” generated via ICT yields a substantially higher on-state performance in device I vs device II (no Si3N4-coated gate-underlap), an effect that becomes even more significant with increasing contact length lcon, see inset. Hence, device II has low on-state performance and is prone to variability.

Figure 8: NEGF simulation results of undoped Si-NWire-FET illustrated in Figure 7: (a) gate-wrap-around Si-NWire FET ...

Figure 8c shows drain-current versus gate-voltage characteristics of device I and II for an underlap of lcon = 5 nm. The SiO2 gate insulator yields a built-in potential that results in self-blocking FETs at VGS = 0 V. Clearly, device I shows a substantially higher on-state performance, becoming even more obvious with increasing underlap region lcon. The inset of Figure 8c displays the drive current at VGS = −1.5 V, showing that device I exhibits very small current degradation with increasing lcon due to effective “doping” (Si3N4-coating) within the underlap region. In contrast, device II strongly depends on lcon with substantial drive current degradation if lcon increases. Device II only delivers an acceptable performance for lcon < 5 nm which ensues a very large parasitic capacitance and presents a challenge to ULSI processing. Moreover, any variation in lcon translates into a strong variability of drive current. This massive deterioration of device II is caused by the lack of “doping”, yielding a substantial increase in potential barriers (cf. Figure 8b) in particular at the gate-channel/gate-underlap interface and at the Ni–contact–Si interfaces, both depending on lcon (see Supporting Information File 1). Without the energy shift caused by Si3N4-coatings in source/drain, we obtain substantially higher Schottky-barriers for device II, resulting in severely deteriorated device performance. Our simulations underline the great importance of alternatives to conventional doping for increased performance of future ULSI transistors.

Conclusion

We demonstrated quantitatively in theory and experiment that the intrinsic electronic properties of usn-Si can yield p- (n-) type behaviour by shifting the electronic DOS towards (away from) Evac using ultrathin Si3N4- (SiO2-) coatings. The key parameters for this phenomenon are the electron affinities X of N and O together with their IOB and bond length to Si. Using NEGF device simulations we compared two undoped Si-NWire-FETs with SiO2- or Si3N4-coating in the source/drain regions and SiO2-coated gate area. We demonstrated that devices with Si3N4-coating exhibit substantially better on-state performance and strongly reduced dependence on the length of the source/drain regions, showing that high performance small-scale MISFETs can be realized using undoped ultrathin Si-NWires with a combined SiO2-/Si3N4-coating. Our findings open a whole new vista on Si-based ULSI operating at lower voltages and lower heat loss. Doping-related technological obstacles typical in CMOS technology are bypassed altogether, extending the potential of structural miniaturization down to the Si-crystallization limit of ca. 1.5 nm [15].

Supporting Information

Supporting Information features the comparison of h-DFT results to experimental data, further information on the interface impact on Si nanocrystal electronic structure and its connection to quantum-chemical nature of N and O, details of UPS scans with further reference data, the derivation of charge carrier densities for nonequilibrium Green’s function (NEGF) transport simulation of undoped Si-nanowire MISFET devices and details on NEGF device simulations.

| Supporting Information File 1: Further discussion and data of h-DFT, UPS, and NEGF simulations. | ||

| Format: PDF | Size: 4.4 MB | Download |

Acknowledgements

D. K. acknowledges use of Leonardi mainframe, engineering faculty, use of Abacus mainframe, IMDC, UNSW and funding by the 2018 Theodore-von-Kàrmàn Fellowship of RWTH Aachen University, Germany and by the 2015 UNSW Blue Sky Research Grant. D. K. and D. H. acknowledge funding by 2012, 2014 and 2016 DAAD-Go8 joint research cooperation schemes. D.H. thanks the Alexander von Humboldt Foundation for a Feodor Lynen Fellowship, acknowledges the German Research Foundation (DFG) for funding (HI 1779/3-1) and acknowledges the IMTEK clean room team (RSC) and L. Sancin at Elettra Synchrotron for technical support. N. W., B. B. and J. K. acknowledge support by the Impulse and Networking Fund of the Helmholtz Association.

References

-

Pearson, G. L.; Bardeen, J. Phys. Rev. 1949, 75, 865–883. doi:10.1103/physrev.75.865

Return to citation in text: [1] -

Koelling, S.; Richard, O.; Bender, H.; Uematsu, M.; Schulze, A.; Zschaetzsch, G.; Gilbert, M.; Vandervorst, W. Nano Lett. 2013, 13, 2458–2462. doi:10.1021/nl400447d

Return to citation in text: [1] -

Kambham, A. K.; Kumar, A.; Florakis, A.; Vandervorst, W. Nanotechnology 2013, 24, 275705. doi:10.1088/0957-4484/24/27/275705

Return to citation in text: [1] -

Heitmann, J.; Müller, F.; Zacharias, M.; Gösele, U. Adv. Mater. 2005, 17, 795–803. doi:10.1002/adma.200401126

Return to citation in text: [1] -

Dalpian, G. M.; Chelikowsky, J. R. Phys. Rev. Lett. 2006, 96, 226802. doi:10.1103/physrevlett.96.226802

Return to citation in text: [1] -

Stegner, A. R.; Pereira, R. N.; Lechner, R.; Klein, K.; Wiggers, H.; Stutzmann, M.; Brandt, M. S. Phys. Rev. B 2009, 80, 165326. doi:10.1103/physrevb.80.165326

Return to citation in text: [1] -

Chan, T.-L.; Tiago, M. L.; Kaxiras, E.; Chelikowsky, J. R. Nano Lett. 2008, 8, 596–600. doi:10.1021/nl072997a

Return to citation in text: [1] -

König, D.; Gutsch, S.; Gnaser, H.; Wahl, M.; Kopnarski, M.; Göttlicher, J.; Steininger, R.; Zacharias, M.; Hiller, D. Sci. Rep. 2015, 5, 9702. doi:10.1038/srep09702

Return to citation in text: [1] [2] -

Pereira, R. N.; Almeida, A. J.; Stegner, A. R.; Brandt, M. S.; Wiggers, H. Phys. Rev. Lett. 2012, 108, 126806. doi:10.1103/PhysRevLett.108.126806

Return to citation in text: [1] -

Dingle, R.; Störmer, H. L.; Gossard, A. C.; Wiegmann, W. Appl. Phys. Lett. 1978, 33, 665–667. doi:10.1063/1.90457

Return to citation in text: [1] -

König, D.; Rudd, J. AIP Adv. 2013, 3, 012109. doi:10.1063/1.4789397

Return to citation in text: [1] -

König, D.; Hiller, D.; Gutsch, S.; Zacharias, M.; Smith, S. Sci. Rep. 2017, 7, 46703. doi:10.1038/srep46703

Return to citation in text: [1] -

König, D.; Rudd, J.; Green, M. A.; Conibeer, G. Phys. Rev. B 2008, 78, 035339. doi:10.1103/PhysRevB.78.035339

Return to citation in text: [1] [2] [3] [4] -

König, D.; Hiller, D.; Gutsch, S.; Zacharias, M. Adv. Mater. Interfaces 2014, 1, 1400359. doi:10.1002/admi.201400359

Return to citation in text: [1] [2] [3] [4] [5] [6] -

Schuppler, S.; Friedman, S. L.; Marcus, M. A.; Adler, D. L.; Xie, Y.-H.; Ross, F. M.; Harris, T. D.; Brown, W. L.; Chabal, Y. J.; Brus, L. E.; Citrin, P. H. Phys. Rev. Lett. 1994, 72, 2648–2651. doi:10.1103/physrevlett.72.2648

Return to citation in text: [1] [2] -

Gaussian 03, Revision D.02; Gaussian, Inc.: Wallingford, CT, U.S.A., 2004.

Return to citation in text: [1] -

Gaussian 09, Revision D.01; Gaussian, Inc.: Wallingford, CT, U.S.A., 2012.

Return to citation in text: [1] -

Gordon, M. S.; Binkley, J. S.; Pople, J. A.; Pietro, W. J.; Hehre, W. J. J. Am. Chem. Soc. 1982, 104, 2797–2803. doi:10.1021/ja00374a017

Return to citation in text: [1] -

Becke, A. D. Phys. Rev. A 1988, 38, 3098–3100. doi:10.1103/physreva.38.3098

Return to citation in text: [1] -

Lee, C.; Yang, W.; Parr, R. G. Phys. Rev. A 1988, 37, 785–789. doi:10.1103/PhysRevB.37.785

Return to citation in text: [1] -

Francl, M. M.; Pietro, W. J.; Hehre, W. J.; Binkley, J. S.; Gordon, M. S.; DeFrees, D. J.; Pople, J. A. J. Chem. Phys. 1982, 77, 3654–3665. doi:10.1063/1.444267

Return to citation in text: [1] -

Hiller, D.; López-Vidrier, J.; Gutsch, S.; Zacharias, M.; Wahl, M.; Bock, W.; Brodyanski, A.; Kopnarski, M.; Nomoto, K.; Valenta, J.; König, D. Sci. Rep. 2017, 7, 8337. doi:10.1038/s41598-017-08814-0

Return to citation in text: [1] -

GaussView, 5.0.8; Semichem Inc.: Shawnee Mission, KS, U.S.A., 2009.

Return to citation in text: [1] -

Hiller, D.; Zelenina, A.; Gutsch, S.; Dyakov, S. A.; López-Conesa, L.; López-Vidrier, J.; Estradé, S.; Peiró, F.; Garrido, B.; Valenta, J.; Kořínek, M.; Trojánek, F.; Malý, P.; Schnabel, M.; Weiss, C.; Janz, S.; Zacharias, M. J. Appl. Phys. 2014, 115, 204301. doi:10.1063/1.4878699

Return to citation in text: [1] -

Petaccia, L.; Vilmercati, P.; Gorovikov, S.; Barnaba, M.; Bianco, A.; Cocco, D.; Masciovecchio, C.; Goldoni, A. Nucl. Instrum. Methods Phys. Res., Sect. A 2009, 606, 780–784. doi:10.1016/j.nima.2009.05.001

Return to citation in text: [1] -

Thust, A.; Barthel, J.; Tillmann, K. J. Large-Scale Res. Facil. 2016, 2, A41. doi:10.17815/jlsrf-2-66

Return to citation in text: [1] -

Auth, C. P.; Plummer, J. D. IEEE Electron Device Lett. 1997, 18, 74–76. doi:10.1109/55.553049

Return to citation in text: [1] -

Venugopal, R.; Paulsson, M.; Goasguen, S.; Datta, S.; Lundstrom, M. S. J. Appl. Phys. 2003, 93, 5613–5625. doi:10.1063/1.1563298

Return to citation in text: [1] -

Holleman, A. F.; Wiberg, E.; Wiberg, N. Lehrbuch der Anorganischen Chemie, 101st ed.; Walter deGruyter: Berlin, Germany, 1995.

Return to citation in text: [1] [2] -

The NIST Reference on Constants, Units and Uncertainties – Fundamental Physical Constants (2014 edition). https://physics.nist.gov/cgi-bin/cuu/Value?asil (accessed Aug 16, 2018).

Return to citation in text: [1] -

König, D. AIP Adv. 2016, 6, 085306. doi:10.1063/1.4960994

Return to citation in text: [1] -

Offi, F.; Iacobucci, S.; Vilmercati, P.; Rizzo, A.; Goldoni, A.; Sacchi, M.; Panaccione, G. Phys. Rev. B 2008, 77, 201101. doi:10.1103/PhysRevB.77.201101

Return to citation in text: [1] -

Böer, K. W. Survey of Semiconductor Physics; Van Nostrand Reinhold: New York, NY, U.S.A., 1992; Vol. 2. doi:10.1007/978-94-011-2912-1

Return to citation in text: [1] -

Suk, S. D.; Lee, S.-Y.; Kim, S.-M.; Yoon, E.-J.; Kim, M.-S.; Li, M.; Oh, C. W.; Yeo, K. H.; Kim, S. H.; Shin, D.-S.; Lee, K.-H.; Park, H. S.; Han, J. N.; Park, C. J.; Park, J.-B.; Kim, D.-W.; Park, D.; Ryu, B.-I. High performance 5nm radius Twin Silicon Nanowire MOSFET (TSNWFET) : fabrication on bulk si wafer, characteristics, and reliability. In IEEE InternationalElectron Devices Meeting 2005, 2005; pp 717–720.

Return to citation in text: [1] -

Bangsaruntip, S.; Majumdar, A.; Cohen, G. M.; Engelmann, S. U.; Zhang, Y.; Guillorn, M.; Gignac, L. M.; Mittal, S.; Graham, W. S.; Joseph, E. A.; Klaus, D. P.; Chang, J.; Cartier, E. A.; Sleight, J. W. Gate-all-around silicon nanowire 25-stage CMOS ring oscillators with diameter down to 3 nm. In 2010 Symposium on VLSI Technology, 2010; pp 21–22.

Return to citation in text: [1] -

Wu, Y.; Xiang, J.; Yang, C.; Lu, W.; Lieber, C. M. Nature 2004, 430, 61–65. doi:10.1038/nature02674

Return to citation in text: [1]

| 29. | Holleman, A. F.; Wiberg, E.; Wiberg, N. Lehrbuch der Anorganischen Chemie, 101st ed.; Walter deGruyter: Berlin, Germany, 1995. |

| 29. | Holleman, A. F.; Wiberg, E.; Wiberg, N. Lehrbuch der Anorganischen Chemie, 101st ed.; Walter deGruyter: Berlin, Germany, 1995. |

| 30. | The NIST Reference on Constants, Units and Uncertainties – Fundamental Physical Constants (2014 edition). https://physics.nist.gov/cgi-bin/cuu/Value?asil (accessed Aug 16, 2018). |

| 1. | Pearson, G. L.; Bardeen, J. Phys. Rev. 1949, 75, 865–883. doi:10.1103/physrev.75.865 |

| 5. | Dalpian, G. M.; Chelikowsky, J. R. Phys. Rev. Lett. 2006, 96, 226802. doi:10.1103/physrevlett.96.226802 |

| 6. | Stegner, A. R.; Pereira, R. N.; Lechner, R.; Klein, K.; Wiggers, H.; Stutzmann, M.; Brandt, M. S. Phys. Rev. B 2009, 80, 165326. doi:10.1103/physrevb.80.165326 |

| 18. | Gordon, M. S.; Binkley, J. S.; Pople, J. A.; Pietro, W. J.; Hehre, W. J. J. Am. Chem. Soc. 1982, 104, 2797–2803. doi:10.1021/ja00374a017 |

| 14. | König, D.; Hiller, D.; Gutsch, S.; Zacharias, M. Adv. Mater. Interfaces 2014, 1, 1400359. doi:10.1002/admi.201400359 |

| 4. | Heitmann, J.; Müller, F.; Zacharias, M.; Gösele, U. Adv. Mater. 2005, 17, 795–803. doi:10.1002/adma.200401126 |

| 19. | Becke, A. D. Phys. Rev. A 1988, 38, 3098–3100. doi:10.1103/physreva.38.3098 |

| 20. | Lee, C.; Yang, W.; Parr, R. G. Phys. Rev. A 1988, 37, 785–789. doi:10.1103/PhysRevB.37.785 |

| 15. | Schuppler, S.; Friedman, S. L.; Marcus, M. A.; Adler, D. L.; Xie, Y.-H.; Ross, F. M.; Harris, T. D.; Brown, W. L.; Chabal, Y. J.; Brus, L. E.; Citrin, P. H. Phys. Rev. Lett. 1994, 72, 2648–2651. doi:10.1103/physrevlett.72.2648 |

| 3. | Kambham, A. K.; Kumar, A.; Florakis, A.; Vandervorst, W. Nanotechnology 2013, 24, 275705. doi:10.1088/0957-4484/24/27/275705 |

| 14. | König, D.; Hiller, D.; Gutsch, S.; Zacharias, M. Adv. Mater. Interfaces 2014, 1, 1400359. doi:10.1002/admi.201400359 |

| 34. | Suk, S. D.; Lee, S.-Y.; Kim, S.-M.; Yoon, E.-J.; Kim, M.-S.; Li, M.; Oh, C. W.; Yeo, K. H.; Kim, S. H.; Shin, D.-S.; Lee, K.-H.; Park, H. S.; Han, J. N.; Park, C. J.; Park, J.-B.; Kim, D.-W.; Park, D.; Ryu, B.-I. High performance 5nm radius Twin Silicon Nanowire MOSFET (TSNWFET) : fabrication on bulk si wafer, characteristics, and reliability. In IEEE InternationalElectron Devices Meeting 2005, 2005; pp 717–720. |

| 35. | Bangsaruntip, S.; Majumdar, A.; Cohen, G. M.; Engelmann, S. U.; Zhang, Y.; Guillorn, M.; Gignac, L. M.; Mittal, S.; Graham, W. S.; Joseph, E. A.; Klaus, D. P.; Chang, J.; Cartier, E. A.; Sleight, J. W. Gate-all-around silicon nanowire 25-stage CMOS ring oscillators with diameter down to 3 nm. In 2010 Symposium on VLSI Technology, 2010; pp 21–22. |

| 2. | Koelling, S.; Richard, O.; Bender, H.; Uematsu, M.; Schulze, A.; Zschaetzsch, G.; Gilbert, M.; Vandervorst, W. Nano Lett. 2013, 13, 2458–2462. doi:10.1021/nl400447d |

| 16. | Gaussian 03, Revision D.02; Gaussian, Inc.: Wallingford, CT, U.S.A., 2004. |

| 17. | Gaussian 09, Revision D.01; Gaussian, Inc.: Wallingford, CT, U.S.A., 2012. |

| 36. | Wu, Y.; Xiang, J.; Yang, C.; Lu, W.; Lieber, C. M. Nature 2004, 430, 61–65. doi:10.1038/nature02674 |

| 13. | König, D.; Rudd, J.; Green, M. A.; Conibeer, G. Phys. Rev. B 2008, 78, 035339. doi:10.1103/PhysRevB.78.035339 |

| 14. | König, D.; Hiller, D.; Gutsch, S.; Zacharias, M. Adv. Mater. Interfaces 2014, 1, 1400359. doi:10.1002/admi.201400359 |

| 33. | Böer, K. W. Survey of Semiconductor Physics; Van Nostrand Reinhold: New York, NY, U.S.A., 1992; Vol. 2. doi:10.1007/978-94-011-2912-1 |

| 10. | Dingle, R.; Störmer, H. L.; Gossard, A. C.; Wiegmann, W. Appl. Phys. Lett. 1978, 33, 665–667. doi:10.1063/1.90457 |

| 15. | Schuppler, S.; Friedman, S. L.; Marcus, M. A.; Adler, D. L.; Xie, Y.-H.; Ross, F. M.; Harris, T. D.; Brown, W. L.; Chabal, Y. J.; Brus, L. E.; Citrin, P. H. Phys. Rev. Lett. 1994, 72, 2648–2651. doi:10.1103/physrevlett.72.2648 |

| 14. | König, D.; Hiller, D.; Gutsch, S.; Zacharias, M. Adv. Mater. Interfaces 2014, 1, 1400359. doi:10.1002/admi.201400359 |

| 8. | König, D.; Gutsch, S.; Gnaser, H.; Wahl, M.; Kopnarski, M.; Göttlicher, J.; Steininger, R.; Zacharias, M.; Hiller, D. Sci. Rep. 2015, 5, 9702. doi:10.1038/srep09702 |

| 9. | Pereira, R. N.; Almeida, A. J.; Stegner, A. R.; Brandt, M. S.; Wiggers, H. Phys. Rev. Lett. 2012, 108, 126806. doi:10.1103/PhysRevLett.108.126806 |

| 7. | Chan, T.-L.; Tiago, M. L.; Kaxiras, E.; Chelikowsky, J. R. Nano Lett. 2008, 8, 596–600. doi:10.1021/nl072997a |

| 8. | König, D.; Gutsch, S.; Gnaser, H.; Wahl, M.; Kopnarski, M.; Göttlicher, J.; Steininger, R.; Zacharias, M.; Hiller, D. Sci. Rep. 2015, 5, 9702. doi:10.1038/srep09702 |

| 12. | König, D.; Hiller, D.; Gutsch, S.; Zacharias, M.; Smith, S. Sci. Rep. 2017, 7, 46703. doi:10.1038/srep46703 |

| 32. | Offi, F.; Iacobucci, S.; Vilmercati, P.; Rizzo, A.; Goldoni, A.; Sacchi, M.; Panaccione, G. Phys. Rev. B 2008, 77, 201101. doi:10.1103/PhysRevB.77.201101 |

| 21. | Francl, M. M.; Pietro, W. J.; Hehre, W. J.; Binkley, J. S.; Gordon, M. S.; DeFrees, D. J.; Pople, J. A. J. Chem. Phys. 1982, 77, 3654–3665. doi:10.1063/1.444267 |

| 13. | König, D.; Rudd, J.; Green, M. A.; Conibeer, G. Phys. Rev. B 2008, 78, 035339. doi:10.1103/PhysRevB.78.035339 |

| 14. | König, D.; Hiller, D.; Gutsch, S.; Zacharias, M. Adv. Mater. Interfaces 2014, 1, 1400359. doi:10.1002/admi.201400359 |

| 22. | Hiller, D.; López-Vidrier, J.; Gutsch, S.; Zacharias, M.; Wahl, M.; Bock, W.; Brodyanski, A.; Kopnarski, M.; Nomoto, K.; Valenta, J.; König, D. Sci. Rep. 2017, 7, 8337. doi:10.1038/s41598-017-08814-0 |

| 13. | König, D.; Rudd, J.; Green, M. A.; Conibeer, G. Phys. Rev. B 2008, 78, 035339. doi:10.1103/PhysRevB.78.035339 |

| 14. | König, D.; Hiller, D.; Gutsch, S.; Zacharias, M. Adv. Mater. Interfaces 2014, 1, 1400359. doi:10.1002/admi.201400359 |

| 28. | Venugopal, R.; Paulsson, M.; Goasguen, S.; Datta, S.; Lundstrom, M. S. J. Appl. Phys. 2003, 93, 5613–5625. doi:10.1063/1.1563298 |

| 13. | König, D.; Rudd, J.; Green, M. A.; Conibeer, G. Phys. Rev. B 2008, 78, 035339. doi:10.1103/PhysRevB.78.035339 |

| 26. | Thust, A.; Barthel, J.; Tillmann, K. J. Large-Scale Res. Facil. 2016, 2, A41. doi:10.17815/jlsrf-2-66 |

| 27. | Auth, C. P.; Plummer, J. D. IEEE Electron Device Lett. 1997, 18, 74–76. doi:10.1109/55.553049 |

| 24. | Hiller, D.; Zelenina, A.; Gutsch, S.; Dyakov, S. A.; López-Conesa, L.; López-Vidrier, J.; Estradé, S.; Peiró, F.; Garrido, B.; Valenta, J.; Kořínek, M.; Trojánek, F.; Malý, P.; Schnabel, M.; Weiss, C.; Janz, S.; Zacharias, M. J. Appl. Phys. 2014, 115, 204301. doi:10.1063/1.4878699 |

| 25. | Petaccia, L.; Vilmercati, P.; Gorovikov, S.; Barnaba, M.; Bianco, A.; Cocco, D.; Masciovecchio, C.; Goldoni, A. Nucl. Instrum. Methods Phys. Res., Sect. A 2009, 606, 780–784. doi:10.1016/j.nima.2009.05.001 |

© 2018 König et al.; licensee Beilstein-Institut.

This is an Open Access article under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/4.0). Please note that the reuse, redistribution and reproduction in particular requires that the authors and source are credited.

The license is subject to the Beilstein Journal of Nanotechnology terms and conditions: (https://www.beilstein-journals.org/bjnano)